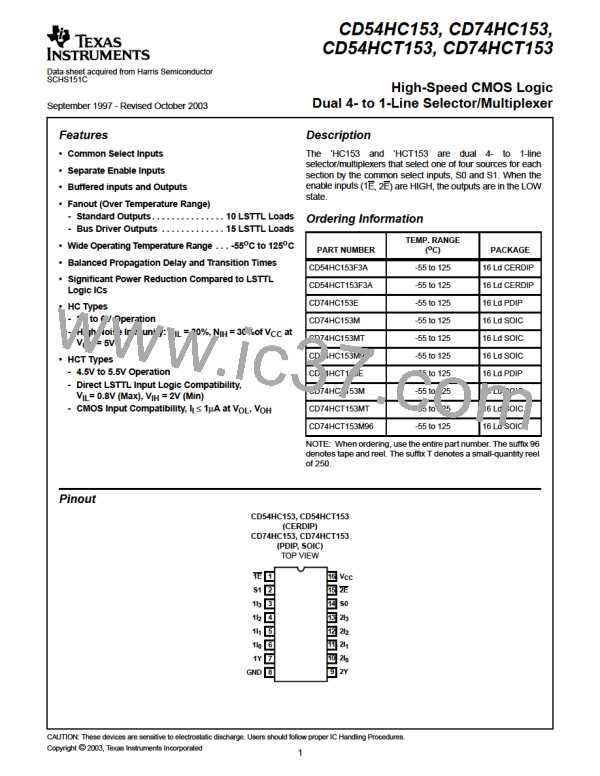

CD54HC153, CD74HC153, CD54HCT153, CD74HCT153

DC Electrical Specifications (Continued)

TEST

CONDITIONS

o

o

o

o

o

25 C

-40 C TO 85 C -55 C TO 125 C

V

CC

PARAMETER

HCT TYPES

SYMBOL

V (V)

I

I

(mA)

(V)

MIN

TYP

MAX

MIN

MAX

MIN

MAX

UNITS

O

High Level Input

Voltage

V

-

-

-

-

4.5 to

5.5

2

-

-

-

-

-

0.8

-

2

-

-

0.8

-

2

-

-

0.8

-

V

V

V

IH

Low Level Input

Voltage

V

4.5 to

5.5

IL

High Level Output

Voltage

CMOS Loads

V

V

V

or V

-0.02

4.5

4.5

4.5

4.5

4.4

4.4

4.4

OH

IH

IH

IL

High Level Output

Voltage

TTL Loads

-4

3.98

-

-

-

-

3.84

-

3.7

-

V

V

V

Low Level Output

Voltage

CMOS Loads

V

or V

0.02

4

-

-

0.1

0.26

-

-

0.1

0.33

-

-

0.1

0.4

OL

IL

Low Level Output

Voltage

TTL Loads

Input Leakage

Current

I

V

and

0

0

-

5.5

5.5

-

-

-

-

-

±0.1

8

-

-

-

±1

80

-

-

-

±1

µA

µA

µA

I

CC

GND

Quiescent Device

Current

I

V

or

160

490

CC

CC

GND

Additional Quiescent

Device Current Per

Input Pin: 1 Unit Load

∆I

CC

(Note 2)

V

4.5 to

5.5

100

360

450

CC

-2.1

NOTE:

2. For dual-supply systems theoretical worst case (V = 2.4V, V

I

= 5.5V) specification is 1.8mA.

CC

HCT Input Loading Table

INPUT

Data

UNIT LOADS

0.45

0.6

Enable

Select

1.35

NOTE: Unit Load is ∆I

360µA max at 25 C.

limit specified in DC Electrical Table, e.g.

CC

o

Switching Specifications Input t , t = 6ns

r

f

o

o

-40 C TO

-55 C TO

o

o

o

25 C

85 C

125 C

TEST

SYMBOL CONDITIONS

V

CC

(V)

PARAMETER

HC TYPES

MIN TYP MAX MIN

MAX

MIN

MAX UNITS

Propagation Delay (Figure 1)

S to Y

t

t

C = 50pF

2

4.5

5

-

-

-

-

-

-

160

32

-

-

-

-

-

200

40

-

-

-

-

-

240

48

-

ns

ns

ns

ns

PLH,

L

PHL

C =15pF

13

-

L

C = 50pF

6

27

34

41

L

4

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]