AM6548, AM6528, AM6526

ZHCSLA7B –DECEMBER 2019 –REVISED JUNE 2021

www.ti.com.cn

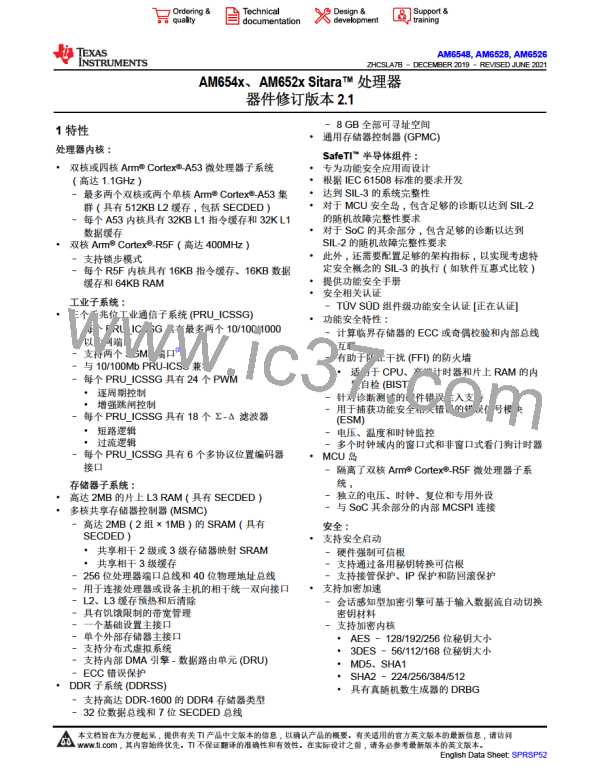

表6-1. Pin Attributes (continued)

BALL

RESET

REL.

RXACTIVE

BALL

RESET

I/O

VOLTAGE

PULL UP/

DOWN

TYPE [12]

BALL NUMBER

MUXMOD

E [4]

BUFFER

TYPE [11]

/

IO Daisy

BALL NAME [2]

SIGNAL NAME [3]

TYPE [5]

POWER [9]

HYS [10]

DSIS [13]

[1]

TXDISABL Chain [15]

E [14]

STATE [6] MUXMOD VALUE [8]

E [7]

R25

GPMC0_CSn2

GPMC0_CSn2

0

O

OFF

7

1.8 V/3.3 V VDDSHV2

Yes

LVCMOS

PU/PD

0/1

Yes

VOUT1_EXTPCLKIN

VIN0_DATA10

1

2

3

4

5

6

I

0

I

0

GPMC0_A27

OZ

I

PRG2_IEP1_EDC_LATCH_IN1

I2C2_SDA

0

1

0

IOD

IO

PRG2_IEP0_EDIO_DATA_IN_OUT3

0

GPIO0_28

7

0

2

3

4

5

6

IO

O

0

0

T27

GPMC0_CSn3

GPMC0_CSn3

VIN0_DATA11

OFF

7

1.8 V/3.3 V VDDSHV2

Yes

LVCMOS

PU/PD

0/1

Yes

I

GPMC0_A26

OZ

O

PRG2_IEP1_EDC_SYNC_OUT1

I2C2_SCL

IOD

IO

1

0

PRG2_IEP0_EDIO_DATA_IN_OUT3

1

GPIO0_29

7

0

1

7

0

1

2

3

4

5

6

IO

I

0

1

R26

R23

GPMC0_WAIT0

GPMC0_WAIT1

GPMC0_WAIT0

VOUT1_DATA22

GPIO0_22

OFF

OFF

7

7

1.8 V/3.3 V VDDSHV2

1.8 V/3.3 V VDDSHV2

Yes

Yes

LVCMOS

LVCMOS

PU/PD

PU/PD

0/1

0/1

Yes

Yes

O

IO

I

0

1

GPMC0_WAIT1

VOUT1_DATA23

VIN0_VD

O

I

0

0

0

0

0

PRG2_PWM1_A0

PRG2_IEP1_EDC_LATCH_IN0

TIMER_IO3

IO

I

IO

IO

PRG2_IEP0_EDIO_DATA_IN_OUT2

8

GPIO0_23

I2C0_SCL

7

0

IO

0

1

D20

C21

B21

I2C0_SCL

I2C0_SDA

I2C1_SCL

IOD

OFF

OFF

OFF

7

7

7

1.8 V/3.3 V VDDSHV0

1.8 V/3.3 V VDDSHV0

1.8 V/3.3 V VDDSHV0

Yes

Yes

Yes

LVCMOS- PU/PD

FS

1/1

1/1

1/1

Yes

Yes

Yes

I2C0_SDA

0

IOD

LVCMOS- PU/PD

FS

1

I2C1_SCL

0

1

0

1

IOD

LVCMOS- PU/PD

FS

1

0

1

0

CPTS0_HW1TSPUSH

I2C1_SDA

I

E21

K2

I2C1_SDA

IOD

OFF

7

1.8 V/3.3 V VDDSHV0

Yes

LVCMOS- PU/PD

FS

1/1

Yes

No

CPTS0_HW2TSPUSH

MCU_ADC0_REFN

I

MCU_ADC0_REFN

A

1.8 V

VDDA_ADC_M

CU

Analog

Copyright © 2021 Texas Instruments Incorporated

22

Submit Document Feedback

Product Folder Links: AM6548 AM6528 AM6526

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]