SMM465

Preliminary Information

I2C 2-WIRE SERIAL INTERFACE AC OPERATING CHARACTERISTICS – 100/400kHz

Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND.

See Figure 4 Timing Diagram.

Conditions

100kHz

Min Typ

400kHz

Min Typ

Symbol Description

Max

Max Units

fSCL

SCL Clock Frequency

0

100

0

400

KHz

tLOW

tHIGH

Clock Low Period

Clock High Period

4.7

4.0

1.3

0.6

µs

µs

Before New Transmission

- Note 1/

tBUF

Bus Free Time

4.7

1.3

µs

Start Condition Setup

Time

tSU:STA

4.7

0.6

µs

tHD:STA

tSU:STO

tAA

Start Condition Hold Time

Stop Condition Setup Time

4.0

4.7

0.6

0.6

µs

µs

SCL low to valid

SDA (cycle n)

SCL low (cycle n+1)

to SDA change

Note 1/

Clock Edge to Data Valid

Data Output Hold Time

0.2

0.2

3.5

0.2

0.2

0.9

µs

tDH

µs

tR

tF

tSU:DAT

tHD:DAT

TI

SCL and SDA Rise Time

SCL and SDA Fall Time

Data In Setup Time

Data In Hold Time

Noise Filter SCL and SDA Noise suppression

Configuration

1000

300

1000

300

ns

ns

ns

ns

ns

Note 1/

250

0

150

0

100

100

tWR_CONFIG Write Cycle Time Config

10

5

10

5

ms

ms

Registers

Memory Array

tWR_EE

Write Cycle Time EE

Note: 1/ - Guaranteed by Design.

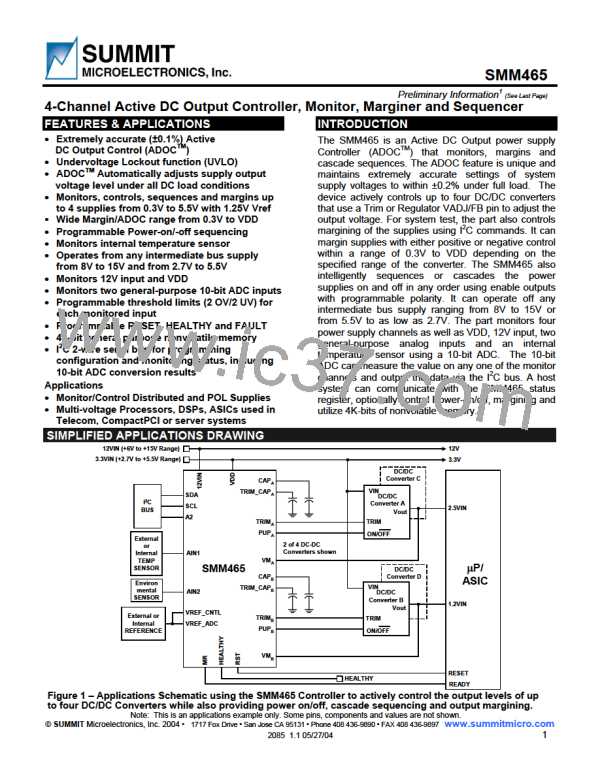

TIMING DIAGRAMS

tWR (For W rite Operation Only)

tHIGH

tLOW

tR

tF

SCL

tBUF

tHD:DAT

tSU:DAT

tSU:SDA

tSU:STO

tHD:SDA

SDA

(IN)

tAA

tDH

SDA

(OUT)

Figure 4 - Basic I2C Serial Interface Timing

Summit Microelectronics, Inc

2085 1.1 05/27/04

11

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]