Description

STM32F103x8, STM32F103xB

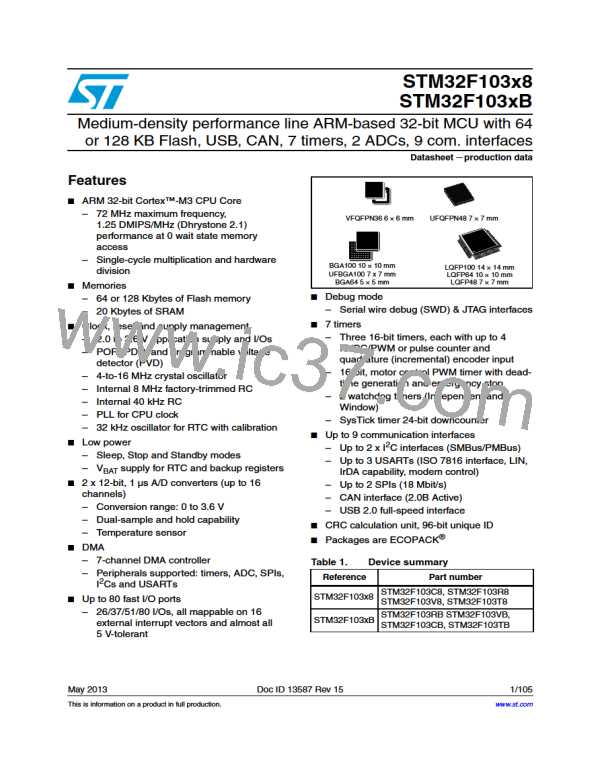

Figure 2.

Clock tree

FLITFCLK

to Flash programming interface

8 MHz

HSI RC

HSI

USBCLK

to USB interface

USB

Prescaler

/1, 1.5

48 MHz

/2

HCLK

72 MHz max

Clock

to AHB bus, core,

memory and DMA

Enable (3 bits)

to Cortex System timer

/8

SW

PLLSRC

FCLK Cortex

free running clock

36 MHz max

PLLMUL

HSI

AHB

Prescaler

/1, 2..512

APB1

Prescaler

/1, 2, 4, 8, 16

SYSCLK

..., x16

x2, x3, x4

PLL

PCLK1

PLLCLK

HSE

72 MHz

max

to APB1

peripherals

Peripheral Clock

Enable (13 bits)

to TIM2, 3

and 4

TIMXCLK

TIM2,3, 4

If (APB1 prescaler =1) x1

else x2

CSS

Peripheral Clock

Enable (3 bits)

APB2

Prescaler

/1, 2, 4, 8, 16

PLLXTPRE

/2

72 MHz max

PCLK2

to APB2

OSC_OUT

OSC_IN

peripherals

4-16 MHz

HSE OSC

Peripheral Clock

Enable (11 bits)

TIM1 timer

If (APB2 prescaler =1) x1

else x2

to TIM1

TIM1CLK

Peripheral Clock

Enable (1 bit)

to ADC

/128

LSE

ADC

Prescaler

/2, 4, 6, 8

OSC32_IN

to RTC

LSE OSC

ADCCLK

RTCCLK

32.768 kHz

OSC32_OUT

RTCSEL[1:0]

to Independent Watchdog (IWDG)

IWDGCLK

LSI

LSI RC

40 kHz

Legend:

HSE = high-speed external clock signal

HSI = high-speed internal clock signal

LSI = low-speed internal clock signal

LSE = low-speed external clock signal

Main

Clock Output

/2

PLLCLK

MCO

HSI

HSE

SYSCLK

MCO

ai14903

1. When the HSI is used as a PLL clock input, the maximum system clock frequency that can be achieved is

64 MHz.

2. For the USB function to be available, both HSE and PLL must be enabled, with USBCLK running at 48

MHz.

3. To have an ADC conversion time of 1 µs, APB2 must be at 14 MHz, 28 MHz or 56 MHz.

12/105

Doc ID 13587 Rev 15

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]