FlashFlex51 MCU

SST89E52RD2 / SST89E54RD2 / SST89E58RD2 / SST89E516RD2

SST89V52RD2 / SST89V54RD2 / SST89V58RD2 / SST89V516RD2

Preliminary Specifications

HIGHEST PRIORITY

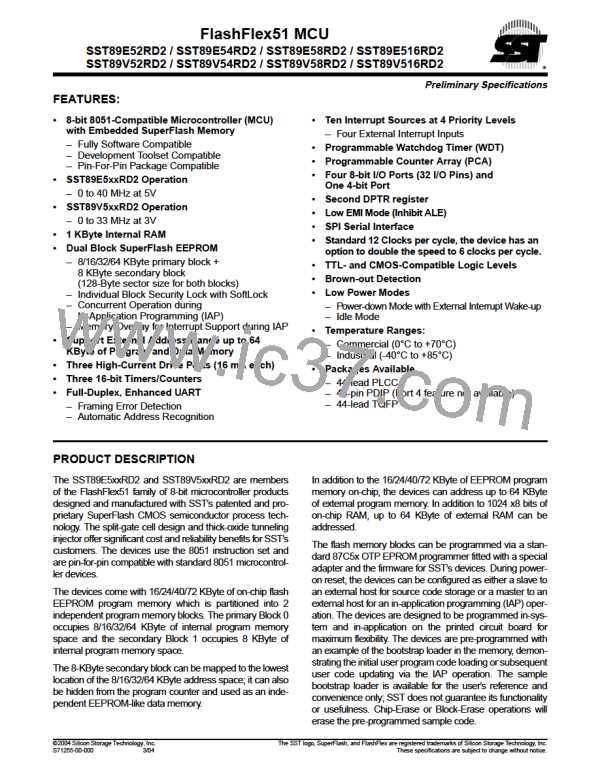

INTERRUPT

IP/IPH/IPA/IPAH

REGISTERS

IE & IEA

REGISTERS

0

1

INT0#

BOF

TF0

IT0

IE0

INTERRUPT

POLLING

SEQUENCE

0

1

INT1#

TF1

IT1

IE1

ECF

CF

CCFn

ECCFn

0

1

INT2#

IT2

IE2

0

1

INT3#

IT3

IE3

RI

TI

SPIF

SPIE

TF2

EXF2

GLOBAL

DISABLE

INDIVIDUAL

ENABLES

LOWEST PRIORITY

INTERRUPT

1255 F31.0

FIGURE 11-1: INTERRUPT STRUCTURE

©2004 Silicon Storage Technology, Inc.

S71255-00-000

3/04

65

SST [ SILICON STORAGE TECHNOLOGY, INC ]

SST [ SILICON STORAGE TECHNOLOGY, INC ]