EFM32G Data Sheet

System Overview

3. System Overview

3.1 System Introduction

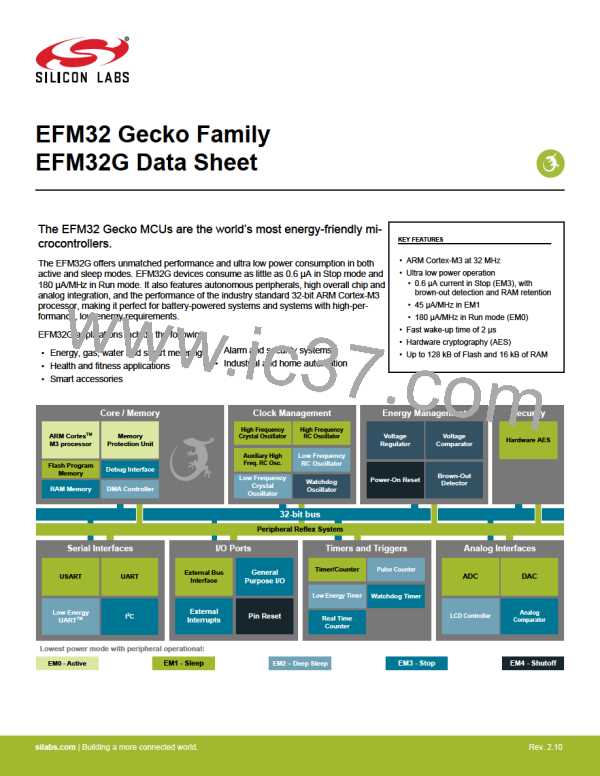

The EFM32 MCUs are the world’s most energy friendly microcontrollers. With a unique combination of the powerful 32-bit ARM Cortex-

M3, innovative low energy techniques, short wake-up time from energy saving modes, and a wide selection of peripherals, the EFM32G

microcontroller is well suited for any battery operated application as well as other systems requiring high performance and low-energy

consumption. This section gives a short introduction to each of the modules in general terms and also shows a summary of the configu-

ration for the EFM32G devices. For a complete feature set and in-depth information on the modules, the reader is referred to the

EFM32G Reference Manual.

The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device fea-

tures, consult Ordering Information.

Core / Memory

Clock Management

Energy Management

Security

High Frequency

Crystal Oscillator

High Frequency

RC Oscillator

ARM CortexTM

M3 processor

Memory

Protection Unit

Voltage

Regulator

Voltage

Comparator

Hardware AES

Low Frequency

RC Oscillator

Auxiliary High

Freq. RC Osc.

Flash Program

Memory

Debug Interface

DMA Controller

Brown-Out

Detector

Low Frequency

Crystal

Oscillator

Power-On Reset

Watchdog

Oscillator

RAM Memory

32-bit bus

Peripheral Reflex System

Serial Interfaces

I/O Ports

Timers and Triggers

Analog Interfaces

Pulse Counter

Timer/Counter

General

External Bus

USART

UART

I2C

ADC

DAC

Interface

Purpose I/O

Low Energy Timer

Watchdog Timer

External

Interrupts

Low Energy

UARTTM

Analog

Comparator

LCD Controller

Pin Reset

Real Time

Counter

Lowest power mode with peripheral operational:

EM0 - Active

EM2 – Deep Sleep

EM1 - Sleep

EM3 - Stop

EM4 - Shutoff

Figure 3.1. Block Diagram

3.1.1 ARM Cortex-M3 Core

The ARM Cortex-M3 includes a 32-bit RISC processor which can achieve as much as 1.25 Dhrystone MIPS/MHz. A Memory Protection

Unit with support for up to 8 memory segments is included, as well as a Wake-up Interrupt Controller handling interrupts triggered while

the CPU is asleep. The EFM32 implementation of the Cortex-M3 is described in detail in EFM32G Reference Manual.

3.1.2 Debug Interface (DBG)

This device includes hardware debug support through a 2-pin serial-wire debug interface . In addition there is also a 1-wire Serial Wire

Viewer pin which can be used to output profiling information, data trace and software-generated messages.

3.1.3 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the EFM32G microcontroller. The flash memory is readable and

writable from both the Cortex-M3 and DMA. The flash memory is divided into two blocks; the main block and the information block.

Program code is normally written to the main block. Additionally, the information block is available for special user data and flash lock

bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations

are supported in the energy modes EM0 and EM1.

silabs.com | Building a more connected world.

Rev. 2.10 | 10