K9F2808U0B-YCB0,YIB0

K9F2808Q0B-DCB0,DIB0

K9F2808U0B-VCB0,VIB0 K9F2808U0B-DCB0,DIB0

FLASH MEMORY

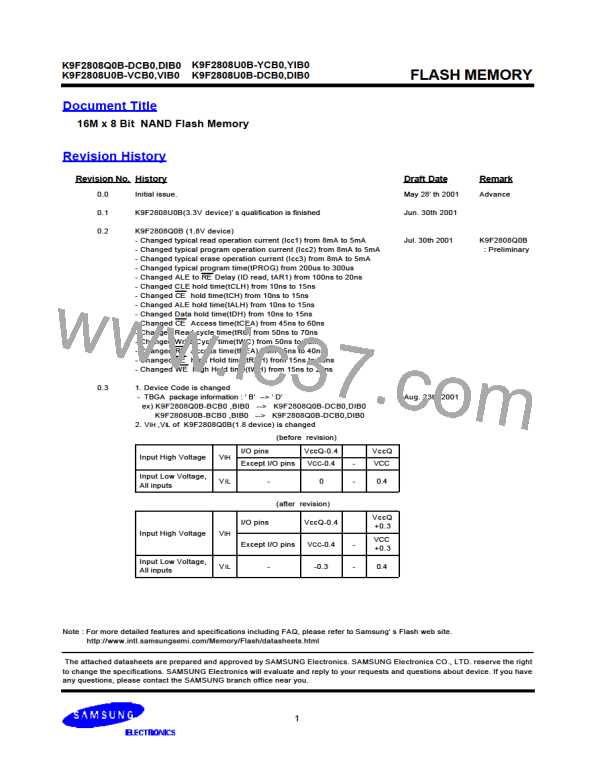

READ ID

The device contains a product identification mode, initiated by writing 90h to the command register, followed by an address input of

00h. Two read cycles sequentially output the manufacture code(ECh), and the device code (73h) respectively. The command register

remains in Read ID mode until further commands are issued to it.

Figure 11 shows the operation sequence.

Figure 11. Read ID Operation

tCLR

CLE

tCEA

CE

WE

tAR1

ALE

tWHR

RE

tREA

Device

Code*

I/O0~7

90h

00h

ECh

Maker code

Address. 1cycle

Device code

Device

Device Code*

K9F2808Q0B

33h

73h

K9F2808U0B

RESET

The device offers a reset feature, executed by writing FFh to the command register. When the device is in Busy state during random

read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no

longer valid, as the data will be partially programmed or erased. The command register is cleared to wait for the next command, and

the Status Register is cleared to value C0h when WP is high. Refer to table 4 for device status after reset operation. If the device is

already in reset state, new reset command will not be accepted by the command register. The R/B pin transitions to low for tRST

after the Reset command is written. Reset command is not necessary for normal operation. Refer to Figure 12 below.

Figure 12. RESET Operation

tRST

R/B

I/O0~7

FFh

Table4. Device Status

After Power-up

After Reset

Operation Mode

Read 1

Waiting for next command

27

SAMSUNG [ SAMSUNG ]

SAMSUNG [ SAMSUNG ]