ib technology

Auxiliary Asynchronous Serial output

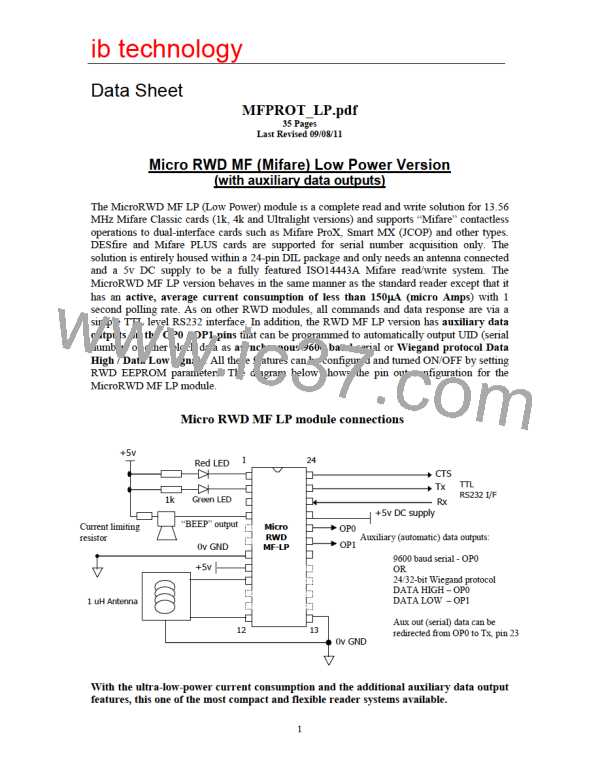

If selected, data can be automatically output from the OP0 or main TX pin as 4-bytes of data

transmitted asynchronously at 9600 baud, 8-bits, 1 stop-bit, no parity. The data source can be

selected as the 4-byte UID (serial number), the least significant 4-bytes of a double UID or

the least significant (first) 4-bytes of a card memory block.

Data bytes transmitted at 9600 baud, 8-bits, 1-stop bit, No parity (104 µS per bit)

b0

1

b1

b2

b3

b4

b5

b6

b7

b8

b9

5v

0v

0

TTL levels

idle START

8 bit data

STOP idle

Auxiliary Wiegand Output Protocol

If selected, data can be automatically output from the OP0 / OP1 pins as Data HIGH and

Data LOW signals according to the Wiegand protocol.

The Wiegand protocol (24 bit data length) can be made up of a leading even parity bit (for b0

- b11), 24 bits of data (from transponder data) and a trailing odd parity bit (for b12- b23)

creating a 26 bit output stream. The 32-bit mode has the same format except least significant

four bytes of block data are used to form the data sequence. The parity bits are included or

omitted and the byte order is reversed according to the EEPROM parameter settings.

For Example:-

Mifare block data (least significant 4 bytes): 0x04 60 22 12

(reversed byte option would use 0x12 22 60 04 as base data)

Wiegand 26 bit sequence:-

E

E

1

(b0 --------- b11) (b12 -------- b23) O

( 0 2 ) O

0000 0100 0110 0000 0010 0010

4

6

0

2

1

Where E is EVEN parity bit for bit 0 to 11 and O is ODD parity bit for bits 12 to 23

The base data for the Wiegand output can be the UID (least significant 4-bytes of serial

number) acquired during the initial ISO14443A communication or the least significant

4-bytes of data from a block of card memory (acquired by an internal Block Read

operation). Selection is by means of an RWD EEPROM parameter.

For the internal Block Read operation, the block number, key code number and type (KeyA or

KeyB) are programmable EEPROM parameters. In addition, parameters control whether the

base data byte order is reversed or if parity bits are added before output.

22

RFSOLUTIONS [ RFSOLUTIONS.LTD ]

RFSOLUTIONS [ RFSOLUTIONS.LTD ]