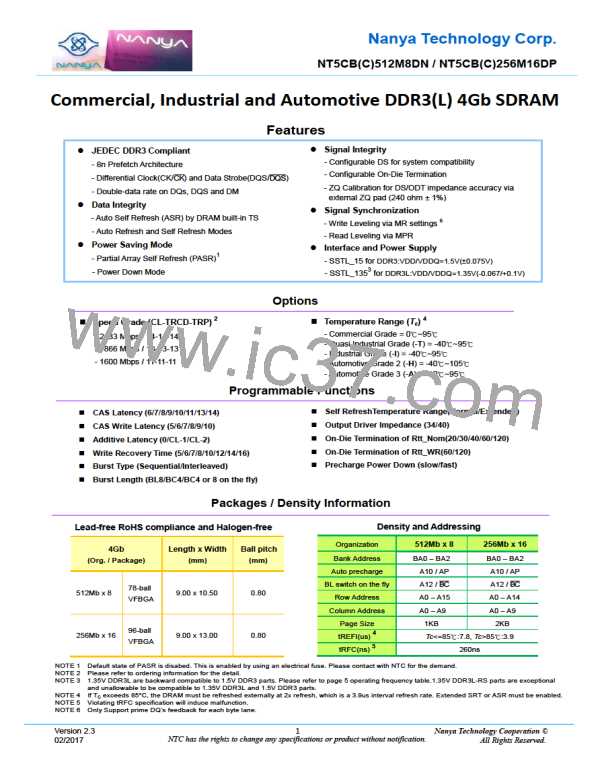

DDR3(L) 4Gb SDRAM

NT5CB(C)512M8DN / NT5CB(C)256M16DP

Descriptions

The 4Gb Double-Data-Rate-3 (DDR3(L)) DRAM is a high-speed CMOS SDRAM containing 4,294,967,296 bits.

It is internally configured as an octal-bank DRAM.

The 4Gb chip is organized as 64Mbit x 8 I/O x 8 banks and 32Mbit x16 I/O x 8 banks. These synchronous

devices achieve high speed double-data-rate transfer rates of up to 2133 Mb/sec/pin for general applications.

The chip is designed to comply with all key DDR3(L) DRAM key features and all of the control and address

inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the cross

point of differential clocks (CK rising and falling). All I/Os are synchronized with a single ended DQS or

differential DQS pair in a source synchronous fashion.

These devices operate with a single 1.5V ± 0.075V or 1.35V -0.067V/+0.1V power supply and are available in

BGA packages.

Version 2.3

02/2017

3

Nanya Technology Cooperation ©

All Rights Reserved.

NANYA [ Nanya Technology Corporation. ]

NANYA [ Nanya Technology Corporation. ]