MITSUBISHI MICROCOMPUTERS

3822 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

On-going Routine

Execute JSR

Interrupt request

(Note)

M (S) (PC

(S) (S) – 1

M (S) (PC

H

)

Push return address

on stack

M (S) (PC

(S) (S) – 1

M (S) (PC

H)

L

)

(S) (S) – 1

M (S) (PS)

(S) (S) – 1

Push return address

on stack

Push contents of processor

status register on stack

L

)

(S) (S)– 1

Subroutine

Interrupt

Service Routine

I Flag is set from “0” to “1”

Execute RTS

(S) (S) + 1

Fetch the jump vector

Execute RTI

(S) (S) + 1

POP return

address from stack

POP contents of

processor status

register from stack

(PC

(S) (S) + 1

(PC M (S)

L)

M (S)

(PS)

(S) (S) + 1

(PC M (S)

(S) (S) + 1

(PC M (S)

M (S)

H)

L)

POP return

address

from stack

H)

Note: Condition for acceptance of an interrupt

Interrupt enable flag is “1”

Interrupt disable flag is “0”

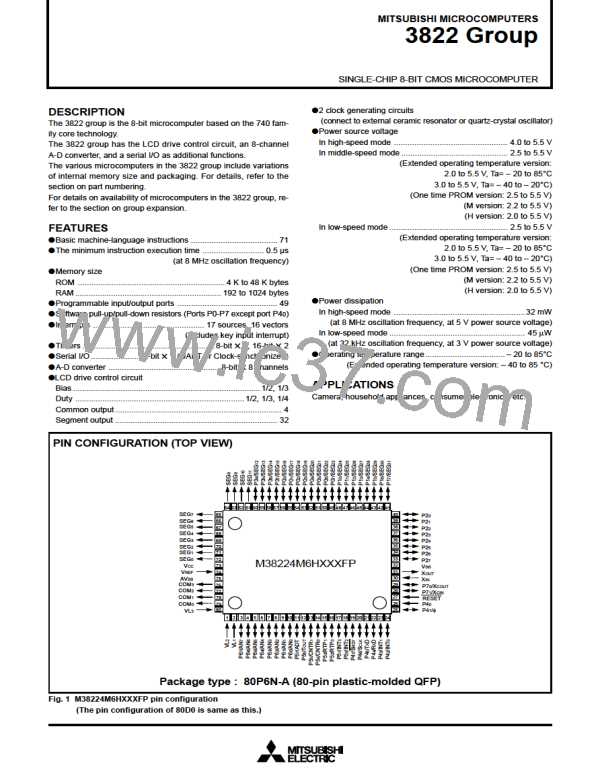

Fig. 10 Register push and pop at interrupt generation and subroutine call

Table 7 Push and pop instructions of accumulator or processor status register

Push instruction to stack

Pop instruction from stack

Accumulator

PHA

PHP

PLA

PLP

Processor status register

12

MITSUBISHI [ Mitsubishi Group ]

MITSUBISHI [ Mitsubishi Group ]