| 型号: | MT9171AN |

| PDF下载: | 下载PDF文件 查看货源 |

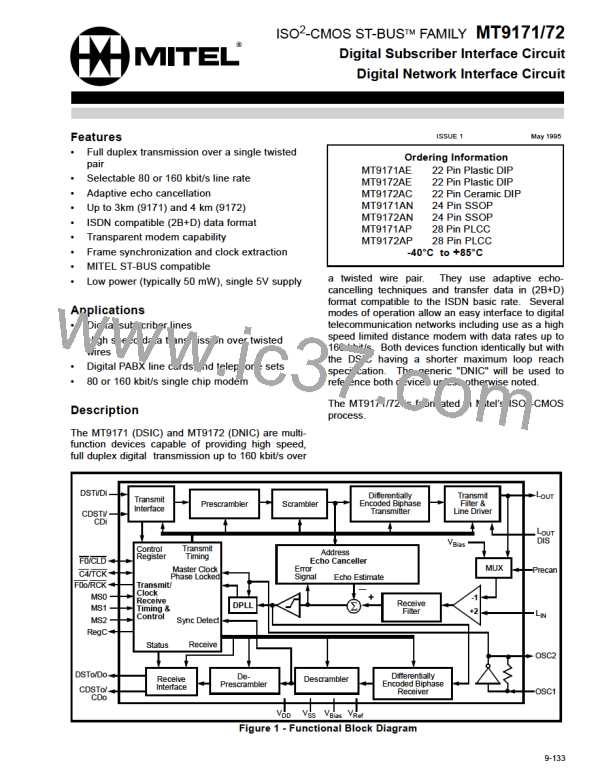

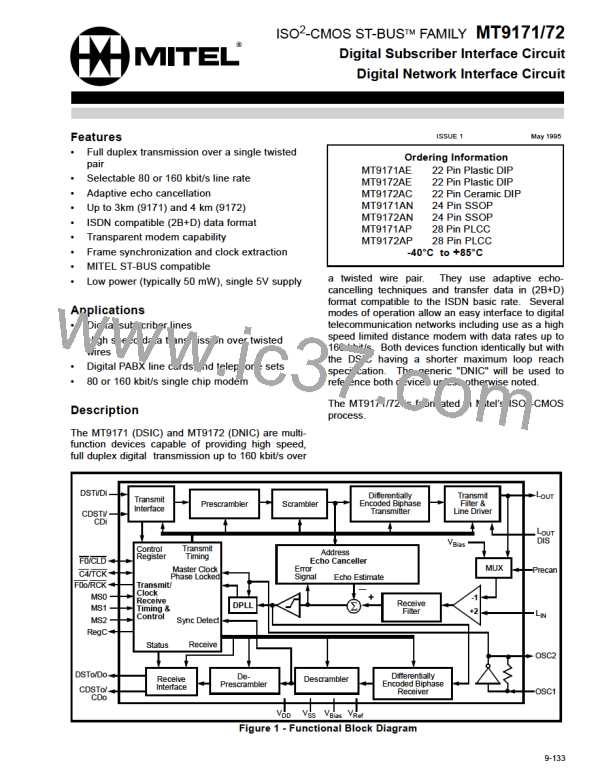

| 内容描述: | ISO2 -CMOS ST- BUS⑩家庭数字用户接口电路数字网络接口电路 [ISO2-CMOS ST-BUS⑩ FAMILY Digital Subscriber Interface Circuit Digital Network Interface Circuit] |

| 分类和应用: | 网络接口电信集成电路光电二极管综合业务数字网 |

| 文件页数/大小: | 22 页 / 396 K |

| 品牌: |  MITEL [ MITEL NETWORKS CORPORATION ] MITEL [ MITEL NETWORKS CORPORATION ] |

专业IC领域供求交易平台:提供全面的IC Datasheet资料和资讯,Datasheet 1000万数据,IC品牌1000多家。