MT9160B/61B

Advance Information

Register Summary

Address

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

TxFG

Bit 1

TxFG

Bit 0

TxFG

Description

00

RxINC

RxFG

RxFG

RxFG

TxINC

Gain Control

Register 1

2

1

0

2

1

0

01

-

-

-

-

-

-

STG

-

STG

-

STG

0

Gain Control

Register 2

2

1

02

03

-

-

-

-

-

DrGain

R Bsel

Path Control

PDFDI

PDDR

RST

T Mute

R Mute

T Bsel

Control

x

x

x

x

Register 1

04

05

CEN

DEN

D8

A/µ

Smag/

ITU-T

CSL

CSL

CSL

0

Control

Register 2

2

1

C

C

D

C

D

C

D

C

C

D

C

D

C

D

C-Channel

Register

7

7

6

5

5

4

4

3

2

2

1

1

0

0

06

D

D

D-Channel

Register

6

3

07y

-

-

-

-

PCM/

loopen

-

-

Loop Back

ANALOG

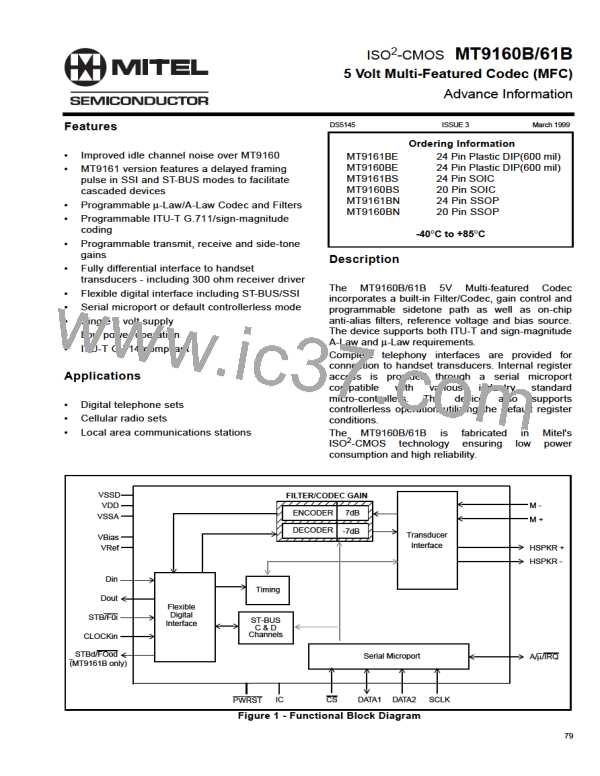

Table 2 - 5V Multi-featured Codec Register Map

Gain Control Register 1

ADDRESS = 00h WRITE/READ VERIFY

Power Reset Value

1000 0000

RxFG RxFG RxFG

TxFG TxFG TxFG

2 1 0

TxINC

3

RxINC

7

2

1

0

6

5

4

2

1

0

Receive Gain

Setting (dB)

Transmit Gain

Setting (dB)

RxFG

RxFG

RxFG

TxFG

TxFG

TxFG

0

2

1

0

2

1

(default) 0

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

(default) 0

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

-1

-2

-3

-4

-5

-6

-7

1

2

3

4

5

6

7

RxFG = Receive Filter Gain bit n

TxFG = Transmit Filter Gain bit n

n

n

RxINC: When high, the receive path nominal gain is set to 0 dB. When low, this gain is -6.0 dB.

TxINC: When high, the transmit nominal gain is set to 15.3 dB. When low, this gain is 6.0 dB.

Note: Bits marked "-" are reserved bits and should be written with logic "0"

89

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]