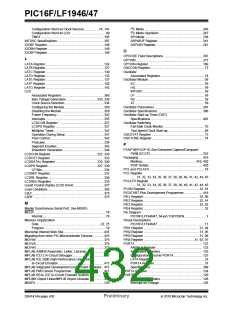

PIC16F/LF1946/47

Timing Diagrams

A/D Conversion......................................................... 404

Type-A in 1/3 Mux, 1/2 Bias Drive............................ 349

Type-A in 1/3 Mux, 1/3 Bias Drive............................ 351

Type-A in 1/4 Mux, 1/3 Bias Drive............................ 353

Type-A/Type-B in Static Drive .................................. 344

Type-B in 1/2 Mux, 1/2 Bias Drive............................ 346

Type-B in 1/2 Mux, 1/3 Bias Drive............................ 348

Type-B in 1/3 Mux, 1/2 Bias Drive............................ 350

Type-B in 1/3 Mux, 1/3 Bias Drive............................ 352

Type-B in 1/4 Mux, 1/3 Bias Drive............................ 354

USART Synchronous Receive (Master/Slave)......... 406

USART Synchronous Transmission

A/D Conversion (Sleep Mode) .................................. 404

Acknowledge Sequence ........................................... 274

Asynchronous Reception.......................................... 297

Asynchronous Transmission..................................... 292

Asynchronous Transmission (Back to Back) ............ 293

Auto Wake-up Bit (WUE) During Normal Operation . 307

Auto Wake-up Bit (WUE) During Sleep .................... 307

Automatic Baud Rate Calculator............................... 306

Baud Rate Generator with Clock Arbitration............. 267

BRG Reset Due to SDA Arbitration During

Start Condition .................................................. 278

Brown-out Reset (BOR)............................................ 400

Brown-out Reset Situations ........................................ 77

Bus Collision During a Repeated Start Condition

(Case 1) ............................................................ 279

Bus Collision During a Repeated Start Condition

(Master/Slave).................................................. 405

Wake-up from Interrupt............................................. 102

Timing Diagrams and Specifications

PLL Clock ................................................................. 397

Timing Parameter Symbology .......................................... 395

Timing Requirements

2

I C Bus Data............................................................. 411

(Case 2) ............................................................ 279

Bus Collision During a Start Condition (SCL = 0) ..... 278

Bus Collision During a Stop Condition (Case 1) ....... 280

Bus Collision During a Stop Condition (Case 2) ....... 280

Bus Collision During Start Condition (SDA only) ...... 277

Bus Collision for Transmit and Acknowledge............ 276

CLKOUT and I/O....................................................... 398

Clock Synchronization .............................................. 264

Clock Timing ............................................................. 396

Comparator Output ................................................... 173

Enhanced Capture/Compare/PWM (ECCP)............. 402

Fail-Safe Clock Monitor (FSCM)................................. 71

First Start Bit Timing ................................................. 268

Full-Bridge PWM Output........................................... 221

Half-Bridge PWM Output .................................. 219, 225

I2C Bus Start/Stop Bits............................................. 410

SPI Mode.................................................................. 409

TMR0 Register.................................................................... 31

TMR1H Register................................................................. 31

TMR1L Register.................................................................. 31

TMR2 Register.............................................................. 31, 39

TRIS ................................................................................. 380

TRISA Register........................................................... 32, 124

TRISB ............................................................................... 126

TRISB Register........................................................... 32, 127

TRISC............................................................................... 129

TRISC Register........................................................... 32, 130

TRISD............................................................................... 132

TRISD Register........................................................... 32, 133

TRISE ............................................................................... 135

TRISE Register........................................................... 32, 136

TRISF ............................................................................... 138

TRISF Register........................................................... 37, 140

TRISG............................................................................... 142

TRISG Register .......................................................... 37, 143

Two-Speed Clock Start-up Mode........................................ 68

TX2REG Register............................................................... 40

TX2STA Register................................................................ 40

TXCON (Timer2/4/6) Register .......................................... 205

TXREG ............................................................................. 291

TXREG Register................................................................. 34

TXSTA Register.......................................................... 34, 298

BRGH Bit.................................................................. 301

2

I C Bus Data............................................................. 410

2

I C Bus Start/Stop Bits.............................................. 409

2

I C Master Mode (7 or 10-Bit Transmission) ............ 271

2

I C Master Mode (7-Bit Reception)........................... 273

2

I C Stop Condition Receive or Transmit Mode......... 275

INT Pin Interrupt.......................................................... 87

Internal Oscillator Switch Timing................................. 66

LCD Interrupt Timing in Quarter-Duty Cycle Drive.... 356

LCD Sleep Entry/Exit when SLPEN = 1

or CS = 00......................................................... 358

PWM Auto-shutdown ................................................ 224

Firmware Restart .............................................. 224

PWM Direction Change ............................................ 222

PWM Direction Change at Near 100% Duty Cycle... 223

PWM Output (Active-High)........................................ 217

PWM Output (Active-Low) ........................................ 218

Repeat Start Condition.............................................. 269

Reset Start-up Sequence............................................ 79

Reset, WDT, OST and Power-up Timer ................... 399

Send Break Character Sequence ............................. 308

SPI Master Mode (CKE = 1, SMP = 1) ..................... 407

SPI Mode (Master Mode).......................................... 241

SPI Slave Mode (CKE = 0) ....................................... 408

SPI Slave Mode (CKE = 1) ....................................... 408

Synchronous Reception (Master Mode, SREN) ....... 313

Synchronous Transmission....................................... 310

Synchronous Transmission (Through TXEN) ........... 310

Timer0 and Timer1 External Clock ........................... 401

Timer1 Incrementing Edge........................................ 195

Two Speed Start-up.................................................... 69

Type-A in 1/2 Mux, 1/2 Bias Drive ............................ 345

Type-A in 1/2 Mux, 1/3 Bias Drive ............................ 347

U

USART

Synchronous Master Mode

Requirements, Synchronous Receive .............. 406

Requirements, Synchronous Transmission...... 406

Timing Diagram, Synchronous Receive ........... 406

Timing Diagram, Synchronous Transmission... 405

V

VREF. SEE ADC Reference Voltage

W

Wake-up on Break............................................................ 306

Wake-up Using Interrupts................................................. 102

Watchdog Timer (WDT)...................................................... 78

Modes....................................................................... 104

Specifications ........................................................... 401

WCOL....................................................... 267, 270, 272, 274

WCOL Status Flag.................................... 267, 270, 272, 274

2010 Microchip Technology Inc.

Preliminary

DS41414A-page 433

MICROCHIP [ MICROCHIP ]

MICROCHIP [ MICROCHIP ]