ClockWorks™

SY100S838

SY100S838L

(÷1, ÷2/3) OR (÷2, ÷4/6)

CLOCK GENERATION CHIP

FEATURES

DESCRIPTION

ꢀ 3.3V and 5V power supply options

ꢀ 50ps output-to-output skew

The SY100S838/L is a low skew (÷1, ÷2/3) or (÷2, ÷4/

6) clock generation chip designed explicitly for low skew

clock generation applications. The internal dividers are

synchronous to each other, therefore, the common output

edges are all precisely aligned. The devices can be driven

by either a differential or single-ended ECL or, if positive

power supplies are used, PECL input signal. In addition,

by using the VBB output, a sinusoidal source can be AC-

coupled into the device. If a single-ended input is to be

used, the VBB output should be connected to the CLK

input and bypassed to ground via a 0.01µF capacitor.

The VBB output is designed to act as the switching

reference for the input of the SY100S838/L under single-

ended input conditions. As a result, this pin can only

source/sink up to 0.5mA of current.

ꢀ Synchronous enable/disable

ꢀ Master Reset for synchronization

ꢀ Internal 75KΩ input pull-down resistors

ꢀ Available in 20-pin SOIC package

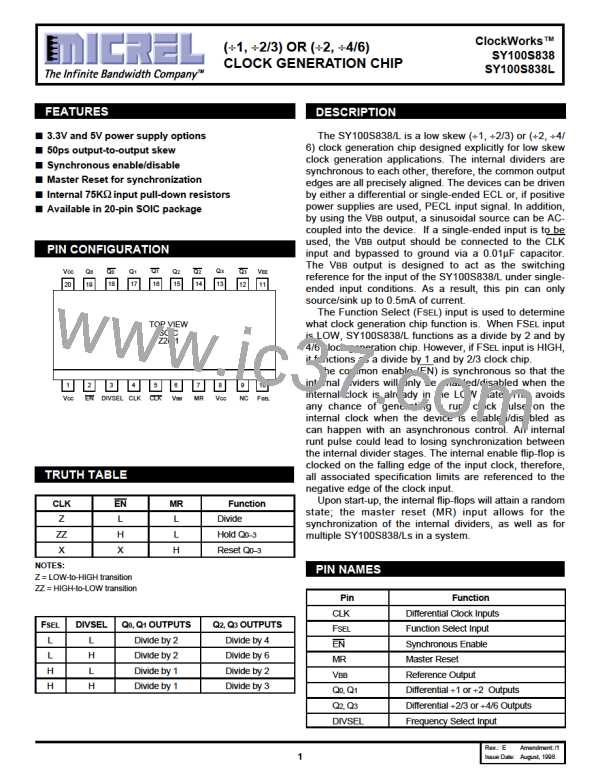

PIN CONFIGURATION

Q

1

Q3

V

CC

Q

0

Q

0

Q

1

Q

2

Q

2

Q

3

VEE

18

17

16

15

14

13

20

19

12

11

The Function Select (FSEL) input is used to determine

what clock generation chip function is. When FSEL input

is LOW, SY100S838/L functions as a divide by 2 and by

4/6 clock generation chip. However, if FSEL input is HIGH,

it functions as a divide by 1 and by 2/3 clock chip.

The common enable (EN) is synchronous so that the

internal dividers will only be enabled/disabled when the

internal clock is already in the LOW state. This avoids

any chance of generating a runt clock pulse on the

internal clock when the device is enabled/disabled as

can happen with an asynchronous control. An internal

runt pulse could lead to losing synchronization between

the internal divider stages. The internal enable flip-flop is

clocked on the falling edge of the input clock, therefore,

all associated specification limits are referenced to the

negative edge of the clock input.

TOP VIEW

SOIC

Z20-1

1

2

3

4

5

6

7

8

9

10

V

CC

EN DIVSEL CLK CLK

V

BB

MR

V

CC

NC

FSEL

TRUTH TABLE

Upon start-up, the internal flip-flops will attain a random

state; the master reset (MR) input allows for the

synchronization of the internal dividers, as well as for

multiple SY100S838/Ls in a system.

CLK

Z

EN

L

MR

L

Function

Divide

ZZ

X

H

L

Hold Q0–3

X

H

Reset Q0–3

NOTES:

PIN NAMES

Z = LOW-to-HIGH transition

ZZ = HIGH-to-LOW transition

Pin

CLK

Function

Differential Clock Inputs

Function Select Input

Synchronous Enable

Master Reset

FSEL

L

DIVSEL

Q0, Q1 OUTPUTS

Divide by 2

Q2, Q3 OUTPUTS

Divide by 4

FSEL

EN

L

H

L

L

Divide by 2

Divide by 6

MR

H

Divide by 1

Divide by 2

VBB

Reference Output

H

H

Divide by 1

Divide by 3

Q0, Q1

Q2, Q3

DIVSEL

Differential ÷1 or ÷2 Outputs

Differential ÷2/3 or ÷4/6 Outputs

Frequency Select Input

Rev.: E

Amendment:/1

Issue Date: August, 1998

1

MICREL [ MICREL SEMICONDUCTOR ]

MICREL [ MICREL SEMICONDUCTOR ]