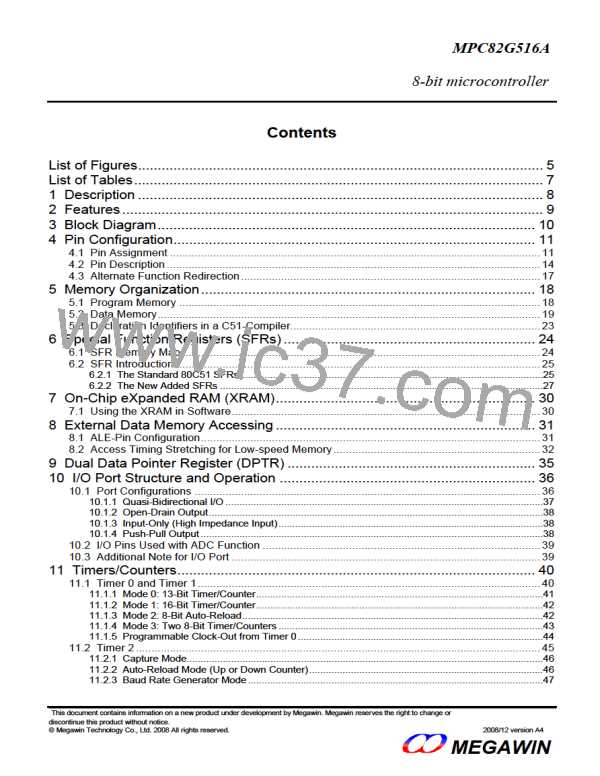

11.2 Timer 2

Timer 2 is a 16-bit Timer/Counter which can operate either as a timer or an event counter, as selected by C/-T2

in the special function register T2CON. Timer 2 has four operating modes: Capture, Auto-Reload (up or down

counting), Baud Rate Generator and Programmable Clock-Out, which are selected by bits in the special function

registers T2CON and T2MOD, as shown below.

T2CON (Address=C8H, Timer/Counter 2 Control Register, Reset Value=0000,0000B)

7

6

5

4

3

2

1

0

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C/-T2 CP/-RL2

TF2: Timer 2 overflow flag set by a Timer 2 overflow and must be cleared by software. TF2 will not be set when

either RCLK=1 or TCLK=1.

EXF2: Timer 2 external flag set when either a capture or reload is caused by a negative transition on T2EX and

EXEN2=1. When Timer 2 interrupt is enabled, EXF2=1 will cause the CPU to vector to the Timer 2 interrupt

routine. EXF2 must be cleared by software. EXF2 does not cause an interrupt in up/down counter mode

(DCEN=1).

RCLK: Receive clock control bit. When set, causes the serial port to use Timer 2 overflow pulses for its receive

clock in serial port Modes 1 and 3. RCLK=0 causes Timer 1 overflow to be used for the receive clock.

TCLK: Transmit clock control bit. When set, causes the serial port to use Timer 2 overflow pulses for its transmit

clock in serial port Modes 1 and 3. TCLK=0 causes Timer 1 overflows to be used for the transmit clock.

EXEN2: Timer 2 external enable bit. When set, allows a capture or reload to occur as a result of a negative

transition on T2EX if Timer 2 is not being used to clock the serial port. EXEN2=0 causes Timer 2 to ignore events

at T2EX.

TR2: Start/stop control for Timer 2. A logic 1 starts the timer.

C/-T2: Timer or counter select. When cleared, select internal timer. When set, select external event counter

(falling edge triggered).

CP/-RL2: Capture/Reload control bit. When set, captures will occur on negative transitions at T2EX if EXEN2=1.

When cleared, auto-reloads will occur either with Timer 2 overflows or negative transitions at T2EX when

EXEN2=1. When either RCLK=1 or TCLK=1, this bit is ignored and the timer is forced to auto-reload on Timer 2

overflow.

T2MOD (Address=C9H, Timer 2 Mode Control Register, Reset Value=xxxx,xx00B)

7

6

5

4

3

2

1

0

-

-

-

-

-

-

T2OE

DCEN

T2OE: Timer 2 clock-out enable bit, set to enable and clear to disable.

DCEN: Timer 2 down-counting enable bit, set to enable and clear to disable.

Table 11-1. Timer 2 Operating Modes

RCLK + TCLK CP/-RL2

TR2

DCEN

T2OE

Mode

x

1

0

0

0

0

x

x

1

0

0

0

0

1

1

1

1

1

x

0

0

0

1

0

0

0

0

0

0

1

(Timer Off)

Baud-rate Generator

16-bit Capture

16-bit Auto-reload (counting-up only)

16-bit Auto-reload (counting-up or counting-down)

Programmable clock-out

45

MPC82G516A Data Sheet

MEGAWIN

MEGAWIN [ MEGAWIN TECHNOLOGY CO., LTD ]

MEGAWIN [ MEGAWIN TECHNOLOGY CO., LTD ]