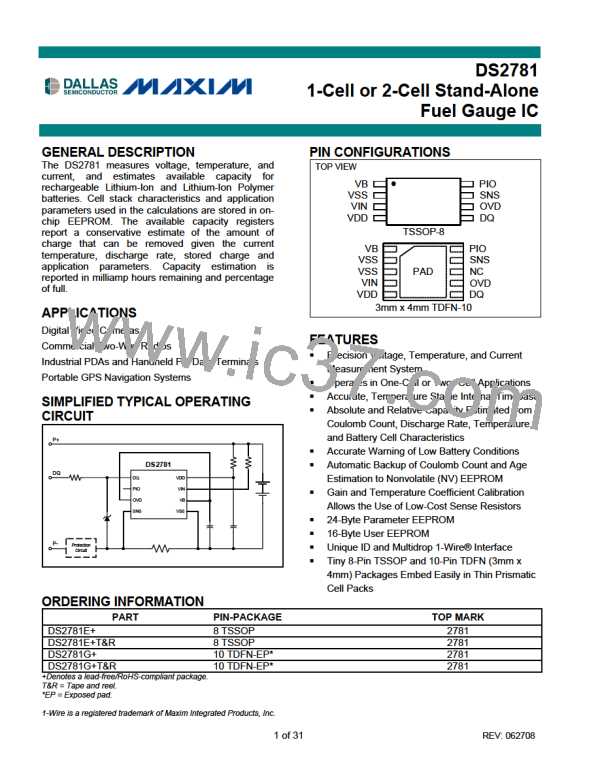

DS2781

STATUS REGISTER

The STATUS register contains bits that report the device status. The bits can be set internally by the DS2781. The

CHGTF, AEF, SEF, LEARNF and VER bits are read only bits that can be cleared by hardware. The UVF and

PORF bits can only be cleared via the 1-Wire interface.

Figure 18. Status Register Format

ADDRESS

FIELD

01h

BIT

BIT DEFINITION

ALLOWABLE VALUES

FORMAT

Charge Termination Flag

Read

Only

Set to 1 when: ( VOLT > VCHG ) AND ( 0 < IAVG < IMIN ) continuously

for a period between two IAVG register updates ( 28s to 56s ).

Cleared to 0 when: RARC < 90%

CHGTF

7

Active Empty Flag

Set to 1 when: VOLT < VAE

Cleared to 0 when: RARC > 5%

Read

Only

AEF

SEF

6

5

Standby Empty Flag

Set to 1 when: RSRC < 10%

Cleared to 0 when: RSRC > 15%

Read

Only

Learn Flag⎯When set to 1, a charge cycle can be used to learn battery

capacity.

Set to 1 when: ( VOLT falls from above VAE to below VAE ) AND

( CURRENT > IAE )

Cleared to 0 when: ( CHGTF = 1 ) OR ( CURRENT < 0 ) OR

( ACR = 0 **) OR ( ACR written or recalled from EEPROM) OR ( SLEEP

Entered )

Read

Only

LEARNF

4

Read

Only

Reserved

3

2

Undefined

Undervoltage Flag

Set to 1 when: VOLT < VSLEEP

Cleared to 0 by: User

Read /

Write *

UVF

Power-On Reset Flag⎯Useful for reset detection, see text below.

Set to 1 upon Power-Up by hardware.

Cleared to 0 by: User

Read /

Write *

PORF

1

0

Read

Only

Reserved

Undefined

* - This bit can be set by the DS2781, and may only be cleared through the 1-Wire interface.

** - LEARNF is only cleared if ACR reaches 0 after VOLT < VAE.

19 of 31

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]