ISL88731A

Undervoltage Detect and Battery Trickle Charging

START and STOP Conditions

If the voltage at CSON falls below 2.5V, the ISL88731A

reduces the charge current limit to 128mA to trickle charge

the battery. When the voltage rises above 2.7V the charge

current reverts to the programmed value in the

ChargeCurrent register.

As shown in Figure 16, START condition is a HIGH-to-LOW

transition of the SDA line while SCL is HIGH.

The STOP condition is a LOW-to-HIGH transition on the SDA

line while SCL is HIGH. A STOP condition must be sent before

each START condition.

Over-Temperature Protection

If the die temperature exceeds +150°C, it stops charging.

Once the die temperature drops below +125°C, charging will

start up again.

SDA

SCL

The System Management Bus

The System Management Bus (SMBus) is a 2-wire bus that

supports bidirectional communications. The protocol is

described briefly here. More detail is available from

www.smbus.org.

S

P

START

CONDITION

STOP

CONDITION

FIGURE 16. START AND STOP WAVEFORMS

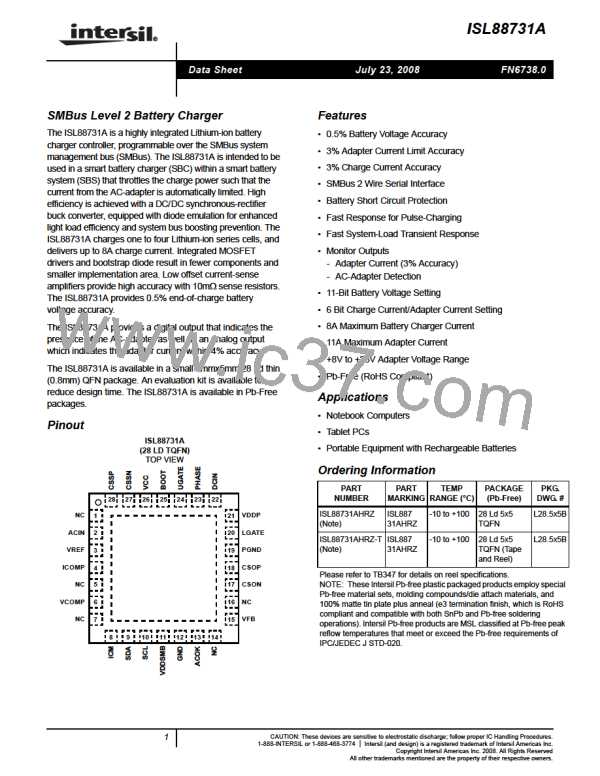

General SMBus Architecture

Acknowledge

VDDSMB

Each address and data transmission uses 9-clock pulses. The

ninth pulse is the acknowledge bit (ACK). After the start

condition, the master sends 7-slave address bits and a R/W bit

during the next 8-clock pulses. During the ninth clock pulse, the

device that recognizes its own address holds the data line low

to acknowledge. The acknowledge bit is also used by both the

master and the slave to acknowledge receipt of register

addresses and data (see Figure 17).

SMBUS SLAVE

INPUT

STATE

MACHINE,

REGISTERS,

MEMORY,

ETC

SCL

OUTPUT

INPUT

CONTROL

SMBUS MASTER

INPUT

SDA

SCL

OUTPUT

INPUT

OUTPUTCONTROL

CONTROL

CPU

SDA

OUTPUT

CONTROL

SMBUS SLAVE

INPUT

OUTPUT

INPUT

SCL

STATE

MACHINE,

REGISTERS,

MEMORY,

ETC

SCL

CONTROL

2

8

1

9

SDA

SDA

OUTPUT

CONTROL

MSB

START

ACKNOWLEDGE

FROM SLAVE

TO OTHER

SLAVE DEVICES

2

FIGURE 17. ACKNOWLEDGE ON THE I C BUS

Data Validity

The data on the SDA line must be stable during the HIGH

period of the SCL, unless generating a START or STOP

condition. The HIGH or LOW state of the data line can only

change when the clock signal on the SCL line is LOW. Refer

to Figure 15.

SMBus Transactions

All transactions start with a control byte sent from the SMBus

master device. The control byte begins with a Start condition,

followed by 7-bits of slave address (0001001 for the

ISL88731A) followed by the R/W bit. The R/W bit is 0 for a write

or 1 for a read. If any slave devices on the SMBus bus

recognize their address, they will Acknowledge by pulling the

serial data (SDA) line low for the last clock cycle in the control

byte. If no slaves exist at that address or are not ready to

communicate, the data line will be 1, indicating a Not

Acknowledge condition.

SDA

SCL

DATA LINE CHANGE

STABLE

DATA VALID ALLOWED

OF DATA

Once the control byte is sent, and the ISL88731A

acknowledges it, the 2nd byte sent by the master must be a

register address byte such as 0x14 for the ChargeCurrent

register. The register address byte tells the ISL88731A

which register the master will write or read. See Table 1 for

details of the registers. Once the ISL88731A receives a

register address byte it responds with an acknowledge.

FIGURE 15. DATA VALIDITY

FN6738.0

July 23, 2008

10

INTERSIL [ Intersil ]

INTERSIL [ Intersil ]