IDT7203/7204/7205/7206/7207/7208CMOSASYNCHRONOUSFIFO

2,048 x 9, 4,096 x 9, 8,192 x 9, 16,384 x 9, 32,768 x 9, 65,536 x 9

COMMERCIAL,INDUSTRIALANDMILITARY

TEMPERATURERANGES

FIFOpermitsareadingofasinglewordafterwritingonewordofdataintoan

emptyFIFO. The data is enabledonthe bus in(tWEF +tA)ns afterthe rising

edgeofW,calledthefirstwriteedge,anditremainsonthebusuntiltheRline

is raisedfromLOW-to-HIGH,afterwhichthebus wouldgointoathree-state

mode after tRHZ ns. The EF line would have a pulse showing temporary

deassertionandthenwouldbeasserted.

Inthewriteflow-throughmode(Figure18),theFIFOpermitsthewritingof

asinglewordofdataimmediatelyafterreadingonewordofdatafromafullFIFO.

TheRlinecausestheFFtobedeassertedbuttheWlinebeingLOWcauses

ittobeassertedagaininanticipationofanewdataword.Ontherisingedgeof

W, the newwordis loadedinthe FIFO. The Wline mustbe toggledwhenFF

isnotassertedtowritenewdataintheFIFOandtoincrementthewritepointer.

USAGEMODES:

Width Expansion

Wordwidthmaybeincreasedsimplybyconnectingthecorrespondinginput

controlsignalsofmultipledevices. Statusflags(EF,FFandHF)canbedetected

fromanyonedevice. Figure13demonstratesan18-bitwordwidthbyusing

twoIDT7203/7204/7205/7206/7207/7208s. Anywordwidthcanbeattained

by adding additional IDT7203/7204/7205/7206/7207/7208s (Figure 13).

Bidirectional Operation

Applications which require data buffering between two systems (each

system capable of Read and Write operations) can be achieved by pairing

IDT7203/7204/7205/7206/7207/7208s as shown in Figure 16. Both Depth

ExpansionandWidthExpansionmaybeusedinthis mode.

Compound Expansion

Thetwoexpansiontechniquesdescribedabovecanbeappliedtogether

in a straightforward manner to achieve large FIFO arrays (see Figure 15).

Data Flow-Through

Twotypesofflow-throughmodesarepermitted,areadflow-throughand

write flow-through mode. For the read flow-through mode (Figure 17), the

(HALF-FULL FLAG)

WRITE (W)

(HF)

READ (R)

9

IDT

7203

7204

7205

7206

7207

7208

9

DATA IN (D)

FULL FLAG (FF)

RESET (RS)

DATA OUT (Q)

EMPTY FLAG (EF)

RETRANSMIT (RT)

2661 drw14

EXPANSION IN (XI)

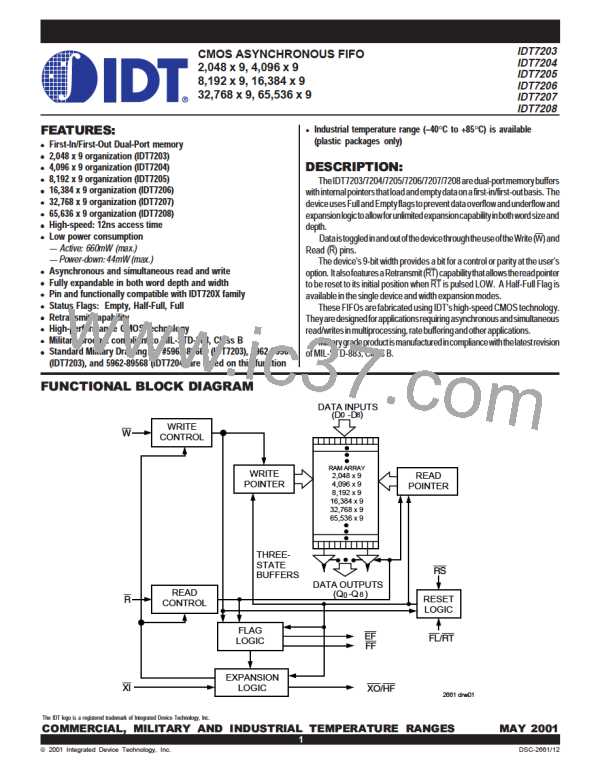

Figure 12. Block Diagram of 2,048 x 9, 4,096 x 9, 8,192 x 9, 16,384 x 9, 32,768 x 9, 65,536 x 9 FIFO Used in Single Device Mode

HF

HF

18

9

9

DATA IN (D)

IDT

WRITE (W)

IDT

READ (R)

7203

7204

7205

7206

7207

7208

7203

7204

7205

7206

7207

7208

FULL FLAG (FF)

RESET (RS)

EMPTY FLAG (EF)

RETRANSMIT (RT)

9

9

XI

XI

18

OUT (Q)

DATA

NOTE:

2661 drw15

1. Flag detection is accomplished by monitoring the FF, EF and HF signals on either (any) device used in the width expansion configuration.

Do not connect any output signals together.

Figure 13. Block Diagram of 2,048 x 18, 4,096 x 18, 8,192 x 18, 16,384 x 18, 32,768 x 18, 65,536 x 18 FIFO Memory Used in Width Expansion Mode

10

IDT [ INTEGRATED DEVICE TECHNOLOGY ]

IDT [ INTEGRATED DEVICE TECHNOLOGY ]