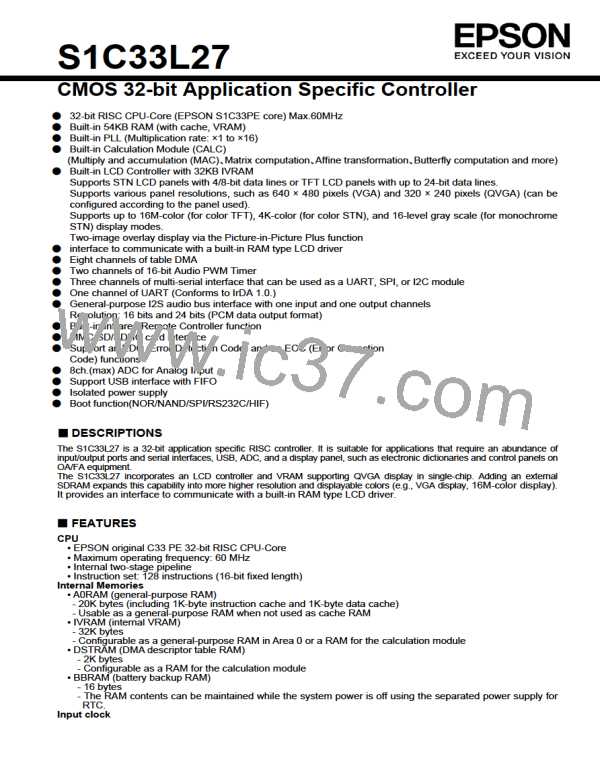

S1C33L27

• High-speed clock (OSC3)

- Maximum input clock frequency: 48 MHz

- Generated by the oscillator circuit (using an external crystal or ceramic resonator) or an external clock is

input.

• Low-speed clock (OSC1)

- 32.768 kHz (typ.) clock for RTC and low-power operations

- Generated by the oscillator circuit (using an external crystal resonator) or an external clock is input.

Cache Controller (CCU)

• 1K-byte instruction cache and 1K-byte data cache that adopts a four-way associative method

• LRU replacement algorithm

• Automatic lock function during debug mode and the interrupt process of specified priority

• Write through function with a 1-word write buffer

DMA Controller (DMAC)

• Eight channels of table DMA

• Supports table reloading and low-priority channel pausing functions.

• 24 hardware trigger sources and 8 software trigger sources

SRAM Controller (SRAMC)

• Allows connection of SRAM, ROM, and Flash memories.

• 26-bit address bus and 8/16-bit selectable data bus

• Up to six chip enable signals are available to connect external devices.

• Up to 64M-byte (A[25:0]) address space can be accessible with each chip enable signal.

• Programmable bus access wait cycle (0 to 15 cycles)

• Little endian access

• Memory mapped I/O

• Supports both A0 and BS (Bus Strobe) type devices.

• Supports external wait request via the #WAIT pin.

SDRAM Controller (SDRAMC)

• Supports SDRAM interface.

• Supports only SDRAM devices with 8/16-bit data bus.

- Minimum configuration: 16M bits (2MB), 16-bit SDRAM × 1

- Maximum configuration: 512M bits (64MB), 16-bit SDRAM × 1

• CAS latency: one, two, or three programmable

• Supports two-burst read and single write operations.

• Equipped with a four-stage × 16-bit DQB (Data Queue Buffer).

• Supports up to four SDRAM banks and bank active mode.

• Built-in 12-bit auto-refresh counter

• Intelligent self-refresh function for low power operation

• Arbitrates external bus accesses by AHB-1 (CPU, DMAC, HIF) and AHB-2 (LCDC).

Host Processor Interface (HIF)

• 8- or 16-bit asynchronous parallel interface to control the S1C33L27 by an external host processor

• Provides semaphore registers.

Clock Management Unit/Oscillators/PLL (CMU)

• Selects the system clock source (OSC3, PLL, or OSC1).

• Turns the OSC3 and OSC1 oscillator circuits on and off.

• Controls frequency multiplication rate of the PLL (×1 to ×16).

• Controls clocks according to the standby mode (SLEEP and HALT).

• Controls the external clock.

• Controls clock supply to the core and peripheral modules.

• OSC3 oscillator circuit

- Crystal oscillation: 5 MHz min. to 48 MHz max.

- Ceramic oscillation: 5 MHz min. to 48 MHz max.

- External clock input: 2 MHz min. to 48 MHz max.

* A 48 MHz clock source with 0.25% of accuracy should be connected for using the USB function.

* Before using a ceramic resonator, please be sure to contact Murata Manufacturing Co., Ltd. for further

information on conditions of use for ceramic resonators.

• PLL

- PLL input frequency: 5 MHz min. to 48 MHz max. (OSC3 ×1, ×1/2, ×1/3, ... ×1/9, ×1/10)

- PLL output frequency: 20 MHz min. to 60 MHz max.

- Multiplication rate: ×1, ×2, ×3, ... ×15, ×16

• OSC1 oscillator circuit

- Crystal oscillation: 32.768 kHz typ.

- External clock input: 32.768 kHz typ.

Interrupt Controller (ITC)

• Five non-maskable interrupts

• 34 maskable interrupts (including four software exceptions)

16-bit Audio PWM Timer (T16P)

• Two channels of 16-bit timer/counter with PWM output function

• Three bit division modes are provided. (10 bits + 6 bits, 9 bits + 7 bits, 8 bits + 8 bits)

• Can support 8, 16, 22.05, 32, 44.1, and 48 kHz sampling rates.

2

EPSON [ EPSON COMPANY ]

EPSON [ EPSON COMPANY ]