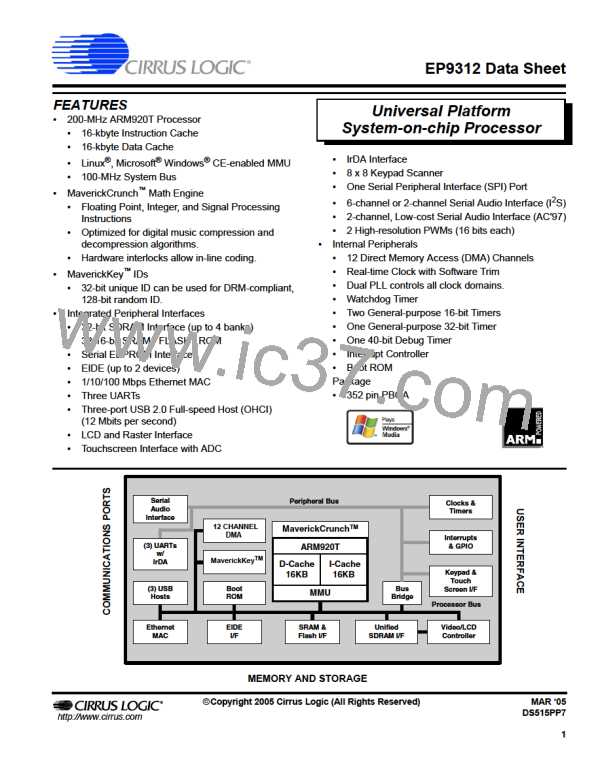

EP9312

Universal Platform SOC Processor

.

Table S. Pin Descriptions (Continued)

Table S. Pin Descriptions

Pad

Type

Pull

Type

Pin Name

RTSn

Block

Description

Pad

Type

Pull

Type

Pin Name

TCK

Block

Description

UART1

UART2

UART2

UART3

UART3

EMAC

EMAC

EMAC

EMAC

EMAC

EMAC

EMAC

EMAC

EMAC

EMAC

EMAC

EMAC

LED

4ma

4ma

I

Ready to send

Transmit / IrDA output

JTAG

JTAG

I

I

PD JTAG clock in

PD JTAG data in

JTAG data out

TXD1

TDI

RXD1

PU Receive / IrDA input

Transmit

TDO

JTAG

4ma

I

TXD2

4ma

I

TMS

JTAG

PD JTAG test mode select

PD JTAG reset

RXD2

PU Receive

TRSTn

JTAG

I

MDC

4ma

4ma

I

Management data clock

PU Management data input/output

PD Receive clock in

PD Receive data in

PD Receive data valid

PD Receive data error

PU Transmit clock in

PD Transmit data out

PD Transmit enable

PD Transmit error

BOOT[1:0]

XTALI

System

PLL

I

PD Boot mode select in

Main oscillator input

MDIO

A

RXCLK

MIIRXD[3:0]

RXDVAL

RXERR

TXCLK

MIITXD[3:0]

TXEN

XTALO

VDD_PLL

GND_PLL

RTCXTALI

RTCXTALO

WRn

PLL

A

Main oscillator output

I

PLL

P

Main oscillator power, 1.8V

Main oscillator ground

RTC oscillator input

I

PLL

G

I

RTC

A

4ma

I

RTC

A

RTC oscillator output

PBUS

PBUS

PBUS

PBUS

PBUS

PBUS

PBUS

PBUS

SDRAM

SDRAM

SDRAM

SDRAM

SDRAM

SDRAM

Raster

Raster

Raster

4ma

4ma

I

SRAM Write strobe out

SRAM Read / OE strobe out

PU SRAM Wait in

4ma

4ma

I

RDn

TXERR

CRS

WAITn

PD Carrier sense

AD[25:0]

DA[31:0]

CSn[3:0]

CSn[7:6]

DQMn[3:0]

SDCLK

SDCLKEN

SDCSn[3:0]

RASn

8ma

8ma

4ma

4ma

8ma

8ma

8ma

4ma

8ma

8ma

8ma

4ma

12ma

8ma

Shared Address bus out

PU Shared Data bus in/out

PU Chip select out

CLD

I

PU Collision detect

Green LED

GRLED

RDLED

EECLK

EEDAT

ABITCLK

ASYNC

ASDI

12ma

12ma

4ma

4ma

8ma

8ma

I

LED

Red LED

PU Chip select out

EEPROM

EEPROM

AC97

AC97

AC97

AC97

AC97

SPI1

PU EEPROM / Two-wire Interface clock

PU EEPROM / Two-wire Interface data

PD AC97 bit clock

PD AC97 frame sync

PD AC97 Primary input

PU AC97 output

Shared data mask out

SDRAM clock out

SDRAM clock enable out

SDRAM chip selects out

SDRAM RAS out

ASDO

8ma

8ma

8ma

8ma

I

CASn

SDRAM CAS out

ARSTn

SCLK1

SFRM1

SSPRX1

SSPTX1

INT[3:0]

PRSTn

RSTOn

SLA[1:0]

EGPIO[15:0]

DD[15:8]

DD7

AC97 reset

SDWEn

P[17:0]

SDRAM write enable out

PU Pixel data bus out

PU Pixel clock in/out

PU Horizontal synchronization / line pulse out

PD SPI bit clock

SPI1

PD SPI Frame Clock

PD SPI input

SPCLK

HSYNC

SPI1

SPI1

8ma

I

SPI output

Vertical or composite synchronization / frame

pulse out

V_CSYNC

Raster

8ma

PU

INT

PD External interrupts

PU Power on reset

User Reset in out - open drain

Flash programming voltage control

Syscon

Syscon

EEPROM

GPIO

IDE

I

BLANK

Raster

Raster

PWM

ADC

8ma

4ma

8ma

A

PU Composite blanking signal out

PWM brightness control out

Pulse width modulator output

Touchscreen ADC X axis

4ma

4ma

BRIGHT

PWMOUT

Xp, Xm

I/O, 4ma PU Enhanced GPIO

8ma

8ma

8ma

8ma

8ma

8ma

8ma

8ma

8ma

I

PU IDE data bus

PD IDE data bus

PU IDE data bus

Yp, Ym

ADC

A

Touchscreen ADC Y axis

IDE

sXp, sXm

sYp, sYm

VDD_ADC

GND_ADC

COL[7:0]

ROW[7:0]

USBp[2:0]

USBm[2:0]

TXD0

ADC

A

Touchscreen ADC X axis feedback

Touchscreen ADC Y axis feedback

Touchscreen ADC power, 3.3V

Touchscreen ADC ground

PU Key matrix column inputs

PU Key matrix row outputs

USB positive signals

DD[6:0]

IDEDA[2:0]

IDECS0n

IDECS1n

DIORn

DIOWn

DMACKn

IORDY

CVDD

IDE

ADC

A

IDE

IDE Device address output

ADC

P

IDE

IDE Chip Select 0 output

IDE Chip Select 1 output

IDE Read strobe output

IDE Write strobe output

IDE DMA acknowledge output

ADC

G

IDE

Key

8ma

8ma

A

IDE

Key

IDE

USB

IDE

USB

A

USB negative signals

IDE

PU IDE ready input

UART1

UART1

UART1

UART1

UART1

4ma

I

Transmit out

Power

Power

Ground

Ground

P

Digital power, 1.8V

Digital power, 3.3V

Digital ground

RXD0

PU Receive in

RVDD

P

CTSn

I

PU Clear to send / transmit enable

PU Data set ready / Data Carrier Detect

Data Terminal Ready output

CGND

G

DSRn

I

RGND

G

Digital ground

DTRn

4ma

DS515PP7

©Copyright 2005 Cirrus Logic (All Rights Reserved)

59

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]