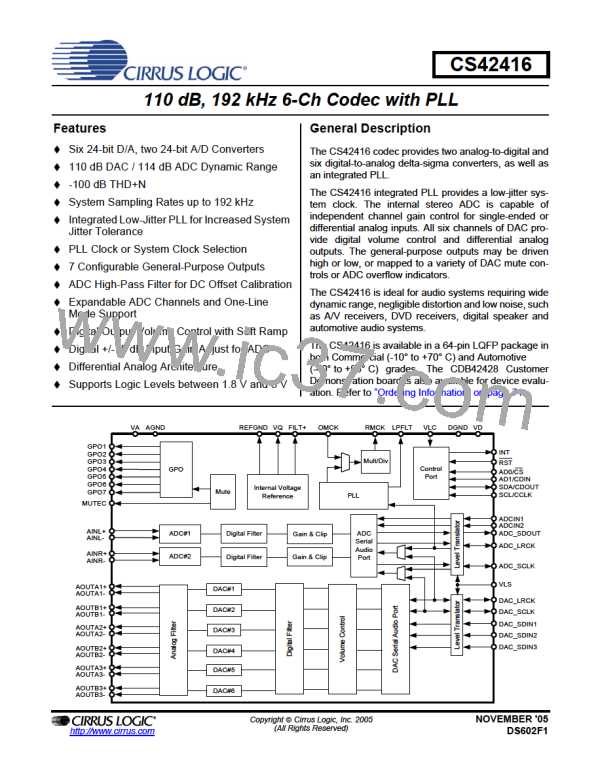

CS42416

6.7

Clock Control (address 06h)

7

6

5

4

3

2

1

0

RMCK_DIV1 RMCK_DIV0 OMCK Freq1 OMCK Freq0

PLL_LRCK

SW_CTRL1

SW_CTRL0 FRC_PLL_LK

6.7.1 RMCK DIVIDE (RMCK_DIVX)

Default = 00

Function:

Divides/multiplies the internal MCLK, either from the PLL or OMCK, by the selected factor.

RMCK_DIV1 RMCK_DIV0

Description

Divide by 1

Divide by 2

Divide by 4

Multiply by 2

0

0

1

1

0

1

0

1

Table 9. RMCK Divider Settings

6.7.2 OMCK FREQUENCY (OMCK FREQX)

Default = 00

Function:

Sets the appropriate frequency for the supplied OMCK.

OMCK Freq1 OMCK Freq0

Description

11.2896 MHz or 12.2880 MHz

16.9344 MHz or 18.4320 MHz

22.5792 MHz or 24.5760 MHz

Reserved

0

0

1

1

0

1

0

1

Table 10. OMCK Frequency Settings

6.7.3 PLL LOCK TO LRCK (PLL_LRCK)

Default = 0

0 - Disabled

1 - Enabled

Function:

When enabled, the internal PLL of the CS42416 will lock to the ADC_LRCK of the ADC serial port

(ADC_LRCK) while the ADC_SP is in Slave Mode.

48

DS602F1

CIRRUS [ CIRRUS LOGIC ]

CIRRUS [ CIRRUS LOGIC ]