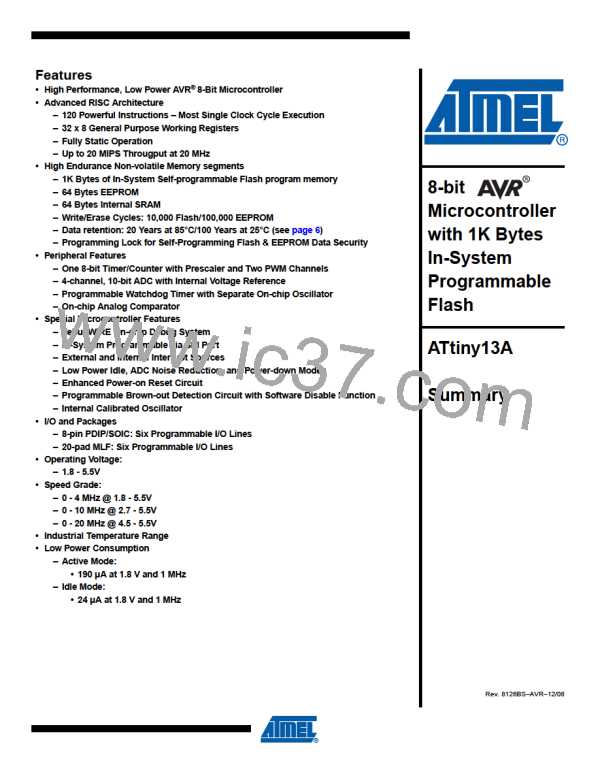

2. Overview

The ATtiny13A is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC

architecture. By executing powerful instructions in a single clock cycle, the ATtiny13A achieves

throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power con-

sumption versus processing speed.

2.1

Block Diagram

Figure 2-1. Block Diagram

8-BIT DATABUS

STACK

POINTER

CALIBRATED

INTERNAL

OSCILLATOR

WATCHDOG

OSCILLATOR

SRAM

WATCHDOG

TIMER

TIMING AND

CONTROL

VCC

GND

MCU CONTROL

REGISTER

PROGRAM

COUNTER

MCU STATUS

REGISTER

PROGRAM

FLASH

TIMER/

COUNTER0

INSTRUCTION

REGISTER

GENERAL

PURPOSE

REGISTERS

INTERRUPT

UNIT

X

Y

Z

PROGRAMMING

LOGIC

INSTRUCTION

DECODER

DATA

EEPROM

CONTROL

LINES

ALU

STATUS

REGISTER

ADC /

ANALOG COMPARATOR

DATA REGISTER

PORT B

DATA DIR.

REG.PORT B

PORT B DRIVERS

RESET

CLKI

PB0-PB5

4

ATtiny13A

8126BS–AVR–12/08

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]