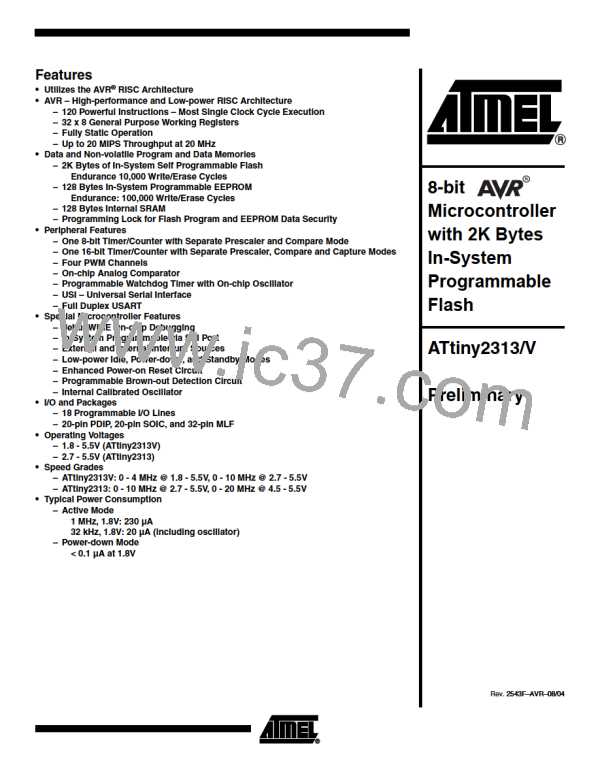

ATtiny2313/V

Pin Descriptions

VCC

Digital supply voltage.

Ground.

GND

Port A (PA2..PA0)

Port A is a 3-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port A output buffers have symmetrical drive characteristics with both high sink

and source capability. As inputs, Port A pins that are externally pulled low will source

current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the ATtiny2313 as listed

on page 52.

Port B (PB7..PB0)

Port D (PD6..PD0)

RESET

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port B output buffers have symmetrical drive characteristics with both high sink

and source capability. As inputs, Port B pins that are externally pulled low will source

current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATtiny2313 as listed

on page 52.

Port D is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each

bit). The Port D output buffers have symmetrical drive characteristics with both high sink

and source capability. As inputs, Port D pins that are externally pulled low will source

current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset

condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATtiny2313 as listed

on page 55.

Reset input. A low level on this pin for longer than the minimum pulse length will gener-

ate a reset, even if the clock is not running. The minimum pulse length is given in Table

15 on page 33. Shorter pulses are not guaranteed to generate a reset. The Reset Input

is an alternate function for PA2 and dW.

XTAL1

XTAL2

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

XTAL1 is an alternate function for PA0.

Output from the inverting Oscillator amplifier. XTAL2 is an alternate function for PA1.

About Code

Examples

This documentation contains simple code examples that briefly show how to use various

parts of the device. These code examples assume that the part specific header file is

included before compilation. Be aware that not all C compiler vendors include bit defini-

tions in the header files and interrupt handling in C is compiler dependent. Please

confirm with the C compiler documentation for more details.

Disclaimer

Typical values contained in this data sheet are based on simulations and characteriza-

tion of other AVR microcontrollers manufactured on the same process technology. Min

and Max values will be available after the device is characterized.

5

2543F–AVR–08/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]