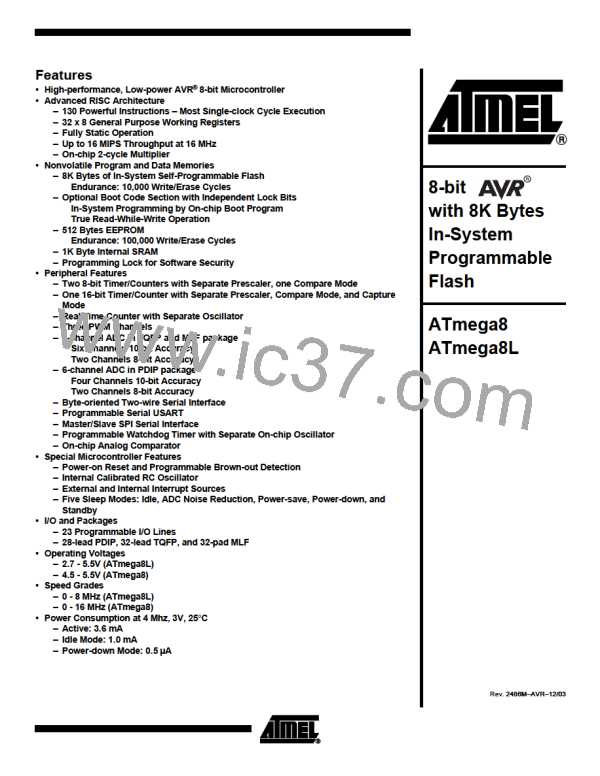

ATmega8(L)

5. This requirement applies to all ATmega8 Two-wire Serial Interface operation. Other

devices connected to the Two-wire Serial Bus need only obey the general fSCL

requirement.

6. The actual low period generated by the ATmega8 Two-wire Serial Interface is (1/fSCL

- 2/fCK), thus fCK must be greater than 6 MHz for the low time requirement to be

strictly met at fSCL = 100 kHz.

7. The actual low period generated by the ATmega8 Two-wire Serial Interface is (1/fSCL

- 2/fCK), thus the low time requirement will not be strictly met for fSCL > 308 kHz when

fCK = 8 MHz. Still, ATmega8 devices connected to the bus may communicate at full

speed (400 kHz) with other ATmega8 devices, as well as any other device with a

proper tLOW acceptance margin.

Figure 115. Two-wire Serial Bus Timing

t

HIGH

t

t

r

of

t

t

LOW

LOW

SCL

SDA

t

t

t

HD;DAT

SU;STA

HD;STA

t

SU;DAT

t

SU;STO

t

BUF

SPI Timing

See Figure 116 and Figure 117 for details.

Characteristics

Table 102. SPI Timing Parameters

Description

SCK period

SCK high/low

Rise/Fall time

Setup

Mode

Master

Master

Master

Master

Master

Master

Master

Master

Slave

Min

Typ

Max

1

2

See Table 50

50% duty cycle

3

3.6

10

4

5

Hold

10

6

Out to SCK

SCK to out

SCK to out high

SS low to out

SCK period

SCK high/low(1)

Rise/Fall time

Setup

0.5 • tSCK

10

7

8

10

9

15

ns

10

11

12

13

14

15

16

17

18

Slave

4 • tck

2 • tck

Slave

Slave

1.6

Slave

10

10

Hold

Slave

SCK to out

SCK to SS high

SS high to tri-state

SS low to SCK

Slave

15

10

Slave

20

Slave

Salve

2 • tck

Note:

1. In SPI Programming mode the minimum SCK high/low period is:

- 2tCLCL for fCK < 12 MHz

- 3tCLCL for fCK > 12 MHz

241

2486M–AVR–12/03

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]