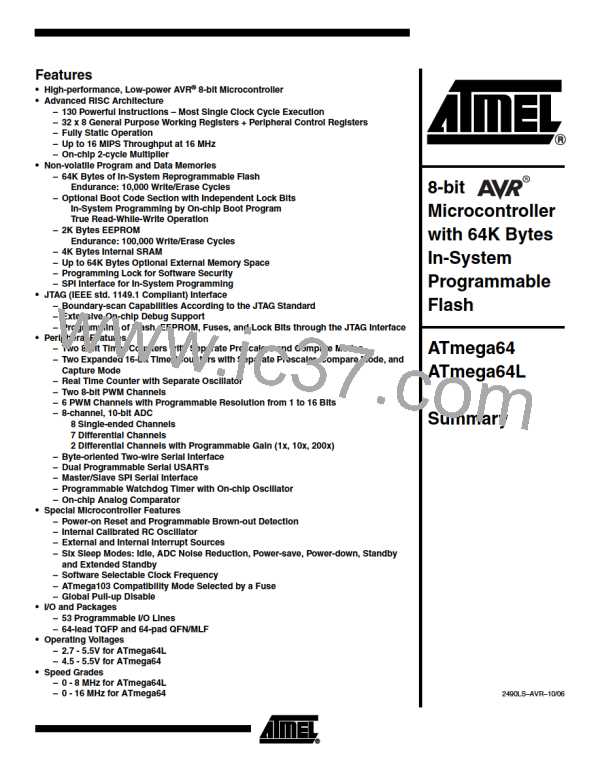

ATmega64(L)

3. Corrected OCn waveforms in Figure 52 on page 127.

4. Various minor Timer1 corrections.

5. Improved the description in “Phase Correct PWM Mode” on page 102 and on

page 155.

6. Various minor TWI corrections.

7. Added note under "Filling the Temporary Buffer (Page Loading)" about writ-

ing to the EEPROM during an SPM page load.

8. Removed ADHSM completely.

9. Added note about masking out unused bits when reading the Program

Counter in “Stack Pointer” on page 14.

10. Added section “EEPROM Write During Power-down Sleep Mode” on page 25.

11. Changed VHYST value to 120 in Table 19 on page 53.

12. Added information about conversion time for Differential mode with Auto

Triggering on page 236.

13. Added tWD_FUSE in Table 128 on page 311.

14. Updated “Packaging Information” on page 15.

Changes from Rev.

2490B-09/02 to Rev.

2490C-09/02

1. Changed the Endurance on the Flash to 10,000 Write/Erase Cycles.

Changes from Rev.

2490A-10/01 to Rev.

2490B-09/02

1. Added 64-pad QFN/MLF Package and updated “Ordering Information” on

page 14.

2. Added the section “Using all Locations of External Memory Smaller than 64

KB” on page 35.

3. Added the section “Default Clock Source” on page 39.

4. Renamed SPMCR to SPMCSR in entire document.

5. Added Some Preliminary Test Limits and Characterization Data

Removed some of the TBD's and corrected data in the following tables and pages:

Table 2 on page 24, Table 7 on page 38, Table 9 on page 41, Table 10 on page 41,

Table 12 on page 42, Table 14 on page 43, Table 16 on page 44, Table 19 on page

53, Table 20 on page 57, Table 22 on page 59, “DC Characteristics” on page 328,

Table 131 on page 330, Table 134 on page 333, Table 136 on page 336, and Table

137 - Table 144.

6. Removed Alternative Algortihm for Leaving JTAG Programming Mode.

See “Leaving Programming Mode” on page 324.

21

2490LS–AVR–10/06

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]