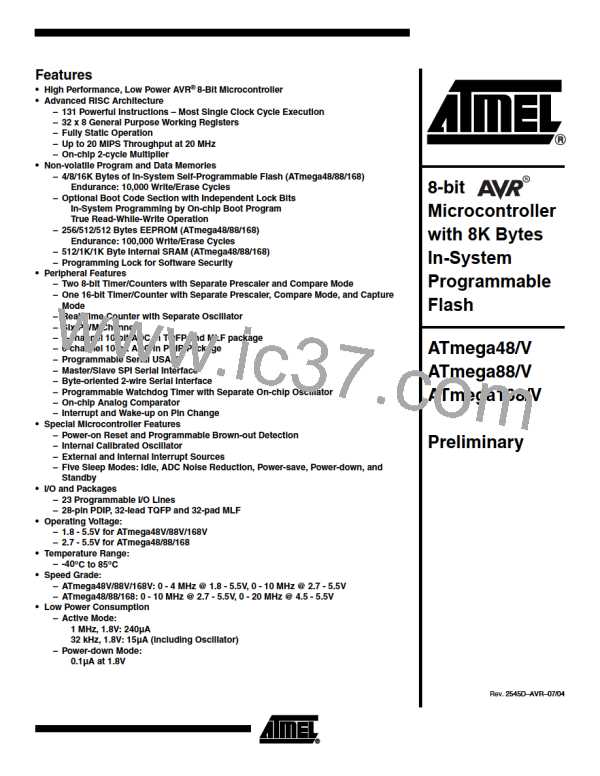

ATmega48/88/168

OCR1A or ICR1 is lower than the current value of TCNT1, the counter will miss the com-

pare match. The counter will then have to count to its maximum value (0xFFFF) and

wrap around starting at 0x0000 before the compare match can occur. In many cases

this feature is not desirable. An alternative will then be to use the fast PWM mode using

OCR1A for defining TOP (WGM13:0 = 15) since the OCR1A then will be double

buffered.

For generating a waveform output in CTC mode, the OC1A output can be set to toggle

its logical level on each compare match by setting the Compare Output mode bits to tog-

gle mode (COM1A1:0 = 1). The OC1A value will not be visible on the port pin unless the

data direction for the pin is set to output (DDR_OC1A = 1). The waveform generated will

have a maximum frequency of fOC A = fclk_I/O/2 when OCR1A is set to zero (0x0000). The

1

waveform frequency is defined by the following equation:

f

clk_I/O

f

= --------------------------------------------------

OCnA

2 ⋅ N ⋅ (1 + OCRnA)

The N variable represents the prescaler factor (1, 8, 64, 256, or 1024).

As for the Normal mode of operation, the TOV1 Flag is set in the same timer clock cycle

that the counter counts from MAX to 0x0000.

Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (WGM13:0 = 5, 6, 7, 14, or 15) pro-

vides a high frequency PWM waveform generation option. The fast PWM differs from

the other PWM options by its single-slope operation. The counter counts from BOTTOM

to TOP then restarts from BOTTOM. In non-inverting Compare Output mode, the Output

Compare (OC1x) is set on the compare match between TCNT1 and OCR1x, and

cleared at TOP. In inverting Compare Output mode output is cleared on compare match

and set at TOP. Due to the single-slope operation, the operating frequency of the fast

PWM mode can be twice as high as the phase correct and phase and frequency correct

PWM modes that use dual-slope operation. This high frequency makes the fast PWM

mode well suited for power regulation, rectification, and DAC applications. High fre-

quency allows physically small sized external components (coils, capacitors), hence

reduces total system cost.

The PWM resolution for fast PWM can be fixed to 8-, 9-, or 10-bit, or defined by either

ICR1 or OCR1A. The minimum resolution allowed is 2-bit (ICR1 or OCR1A set to

0x0003), and the maximum resolution is 16-bit (ICR1 or OCR1A set to MAX). The PWM

resolution in bits can be calculated by using the following equation:

log(TOP + 1)

R

= ----------------------------------

FPWM

log(2)

In fast PWM mode the counter is incremented until the counter value matches either

one of the fixed values 0x00FF, 0x01FF, or 0x03FF (WGM13:0 = 5, 6, or 7), the value in

ICR1 (WGM13:0 = 14), or the value in OCR1A (WGM13:0 = 15). The counter is then

cleared at the following timer clock cycle. The timing diagram for the fast PWM mode is

shown in Figure 47. The figure shows fast PWM mode when OCR1A or ICR1 is used to

define TOP. The TCNT1 value is in the timing diagram shown as a histogram for illus-

trating the single-slope operation. The diagram includes non-inverted and inverted PWM

outputs. The small horizontal line marks on the TCNT1 slopes represent compare

matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a com-

pare match occurs.

117

2545D–AVR–07/04

ATMEL [ ATMEL ]

ATMEL [ ATMEL ]