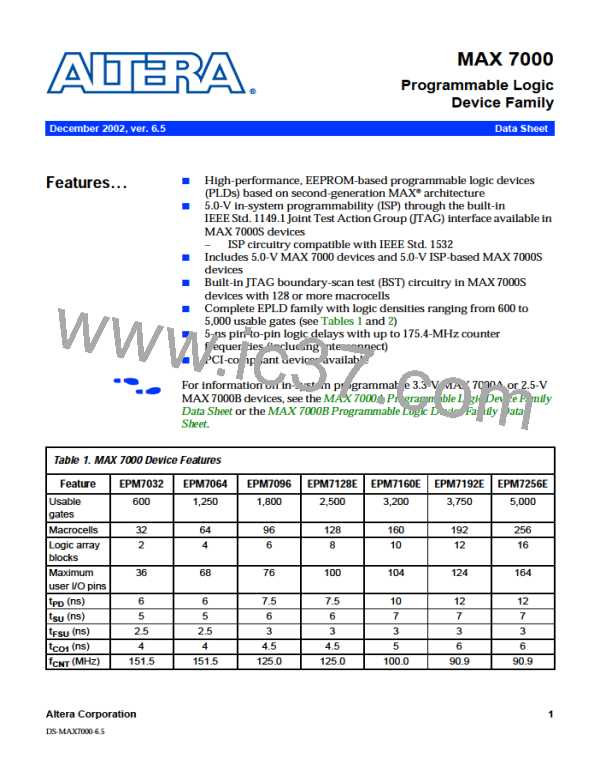

MAX 7000 Programmable Logic Device Family Data Sheet

Table 2. MAX 7000S Device Features

Feature

EPM7032S

EPM7064S

EPM7128S

EPM7160S

EPM7192S

EPM7256S

Usable gates

Macrocells

600

32

2

1,250

64

2,500

128

8

3,200

160

10

3,750

192

12

5,000

256

16

Logic array

blocks

4

Maximum

36

68

100

104

124

164

user I/O pins

tPD (ns)

5

2.9

5

2.9

6

3.4

2.5

4

6

3.4

7.5

4.1

7.5

3.9

t

SU (ns)

tFSU (ns)

2.5

2.5

2.5

3

3

t

f

CO1 (ns)

3.2

3.2

3.9

4.7

4.7

CNT (MHz)

175.4

175.4

147.1

149.3

125.0

128.2

■

■

Open-drain output option in MAX 7000S devices

Programmable macrocell flipflops with individual clear, preset,

clock, and clock enable controls

Programmable power-saving mode for a reduction of over 50% in

each macrocell

Configurable expander product-term distribution, allowing up to

32 product terms per macrocell

...and More

Features

■

■

■

44 to 208 pins available in plastic J-lead chip carrier (PLCC), ceramic

pin-grid array (PGA), plastic quad flat pack (PQFP), power quad flat

pack (RQFP), and 1.0-mm thin quad flat pack (TQFP) packages

Programmable security bit for protection of proprietary designs

3.3-V or 5.0-V operation

■

■

–

MultiVoltTM I/ O interface operation, allowing devices to

interface with 3.3-V or 5.0-V devices (MultiVolt I/ O operation is

not available in 44-pin packages)

–

Pin compatible with low-voltage MAX 7000A and MAX 7000B

devices

■

■

Enhanced features available in MAX 7000E and MAX 7000S devices

–

–

–

–

Six pin- or logic-driven output enable signals

Two global clock signals with optional inversion

Enhanced interconnect resources for improved routability

Fast input setup times provided by a dedicated path from I/ O

pin to macrocell registers

–

Programmable output slew-rate control

Software design support and automatic place-and-route provided by

Altera’s development system for Windows-based PCs and Sun

SPARCstation, and HP 9000 Series 700/ 800 workstations

2

Altera Corporation

ALTERA [ ALTERA CORPORATION ]

ALTERA [ ALTERA CORPORATION ]