[AK1572]

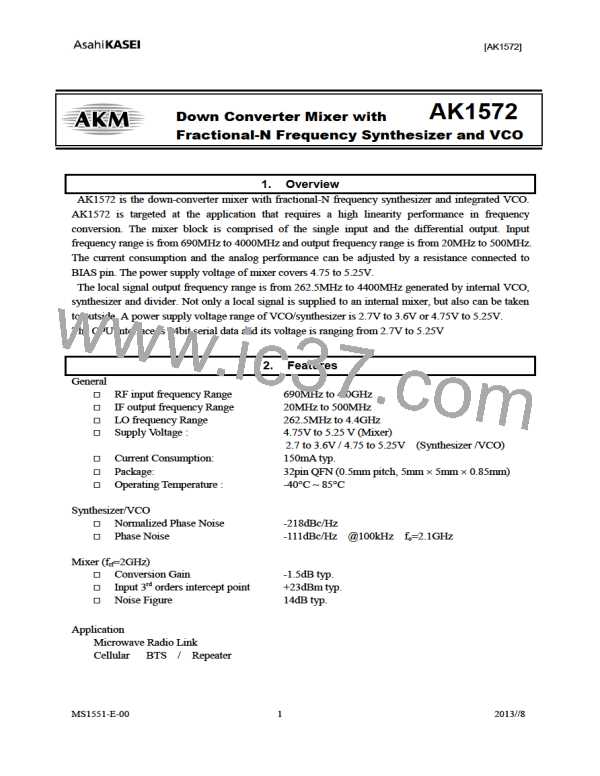

16. Power up Sequence

min. 500usec

min. 10msec

4)

3)

1)

2)

PDN Pin

VDD1, VDD2, VDD3

VREF1(LDO)

Register writing

Prohibit

Active

Lock

Power Down

Power Down

Unstable

VCO calibration

Fast Lock

PLL/Synth

Mixer

Active

1) Set [PDN] pin to “L” and turn on power supplies (VDD1/VDD2/VDD3)

2) The stabilization time for [VREF1] (LDO) is 10msec. After LDO is stabilized, write the data to

the registers of <Address 0x01, 0x02, 0x03, 0x04>

3) Set [PDN] pin to “H”. In this state, the internal circuits are in an operating state, but PLL/Synth

is unstable yet.

4) The stabilization time of internal BIAS circuits is 500usec. After BIAS circuit is stabilized,

write the data to <Address 0x01>. VCO calibration starts and PLL status will be locked. Refer

to 14.Fast Lock Mode and 15.VCO contents regarding fast Lock mode and VCO calibration.

Note1) The initial register values are not defined. Therefore, it is required to write the data in all

addresses of the register.

Note2) The stabilization time for LDO is required more than 10ms.

MS1551-E-00

28

2013/8

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]