[AK1572]

12. Lock Detect

Lock detect output can be selected by {LD} in D [13] of <Address0x04>. When {LD} is set to “1”,

the [LD] pin outputs a phase comparison result which is from phase detector directly. (This is called

“analog lock detect”.) When {LD} is set to “0”, the output is the lock detect signal according to the

on-chip logic. (This is called “digital lock detect”.)

The digital lock detect can be done as following:

The [LD] pin is in unlocked state (which outputs “L”) when a frequency setup is made.

In the digital lock detect, the [LD] pin outputs “H” (which means the locked state) when a phase error

smaller than a cycle of [REFIN] clock (T) is detected for N times consecutively. When a phase error

larger than T is detected for N times consecutively while the [LD] pin outputs “H”, then the [LD] pin

outputs “L” (which means the unlocked state). The counter value N can be set by {LDCNTSEL} in D

[14] of <Address0x04>. The N is different between “unlocked to locked” and “locked to unlocked”.

{LDCNTSEL} unlocked to locked

locked to unlocked

0

1

N=15

N=31

N=3

N=7

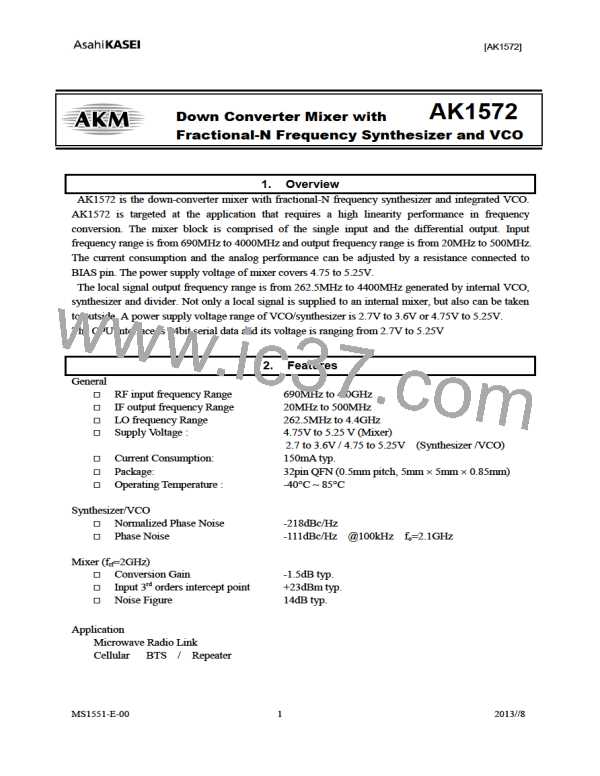

The lock detect signal is shown below

Reference clock

Phase Comparison signal

Divided VCO signal

T/2

Phase detector output signal

ignore

This is ignored because it

cannot be sampled.

Valid

Valid

ignore

ignore

The [LD] pin outputs HIGH when a

phase error which is smaller than T/2

is detected for N times consecutively.

LD output

Case of “R = 1”

MS1551-E-00

22

2013/8

AKM [ ASAHI KASEI MICROSYSTEMS ]

AKM [ ASAHI KASEI MICROSYSTEMS ]