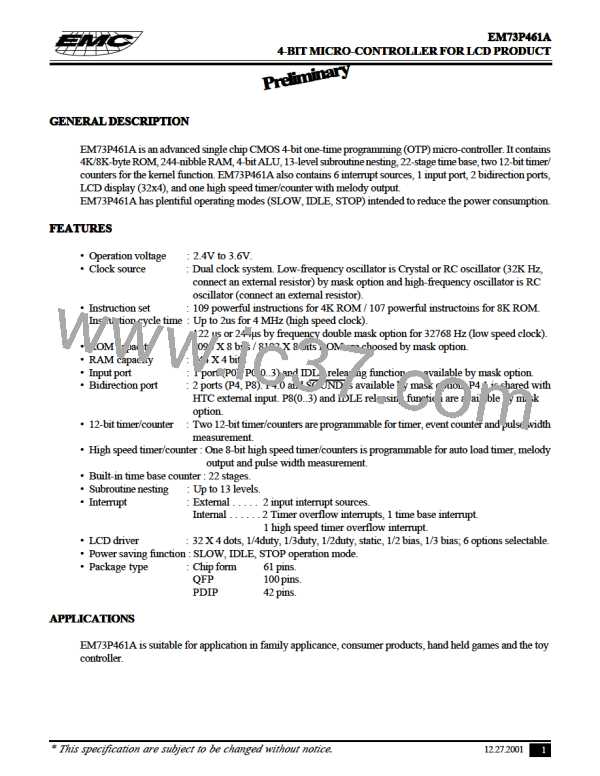

EM73P461A

4-BIT MICRO-CONTROLLER FOR LCD PRODUCT

(10) Input/output

Mnemonic

Object code (binary) Operation description

Byte Cycle

Flag

C

-

-

-

-

Z

Z

-

-

-

S

INA

INM

p

p

0110 1111 0100 pppp

0110 1111 1100 pppp

Acc←PORT[p]

RAM[HL]←PORT[p]

PORT[p]←k

PORT[p]←Acc

PORT[p]←RAM[HL]

2

2

2

2

2

2

2

2

2

2

Z'

Z'

1

1

1

OUT #k,p 0100 1010 kkkk pppp

OUTA p

OUTM p

0110 1111 000p pppp

0110 1111 100p pppp

-

-

(11) Flag manipulation

Mnemonic Object code (binary) Operation description

Byte Cycle

Flag

C

-

-

0

-

1

-

Z

-

-

-

-

S

1

1

*

*

*

*

@ CGF

@ SGF

TFCFC

@ TGS

TTCFS

TZS

0101 0111

0101 0101

0101 0011

0101 0100

0101 0010

0101 1011

GF←0

GF←1

SF←CF', CF←0

SF←GF

SF←CF, CF←1

SF←ZF

1

1

1

1

1

1

1

1

1

1

1

1

-

-

(12) Interrupt control

Mnemonic Object code (binary) Operation description

CIL

Byte Cycle

Flag

C

-

-

-

-

Z

-

-

-

-

*

S

1

1

1

1

*

r

0110 0011 11rr rrrr

0110 0011 10rr rrrr

0110 0011 01rr rrrr

0111 0101

IL←IL & r

2

2

2

1

1

2

2

2

1

2

DICIL r

EICIL r

EXAE

RTI

EIF←0,IL←IL&r

EIF←1,IL←IL&r

MASK↔Acc

SP←SP+1,FLAG.PC

←STACK[SP],EIF ←1

0100 1101

*

(13) CPU control

Mnemonic

NOP

Object code (binary) Operation description

0101 0110 no operation

Byte Cycle

Flag

C

-

Z

-

S

-

1

1

@ : just for 4K ROM

* This specification are subject to be changed without notice.

12.27.2001

36

ELAN [ ELAN MICROELECTRONICS CORP ]

ELAN [ ELAN MICROELECTRONICS CORP ]